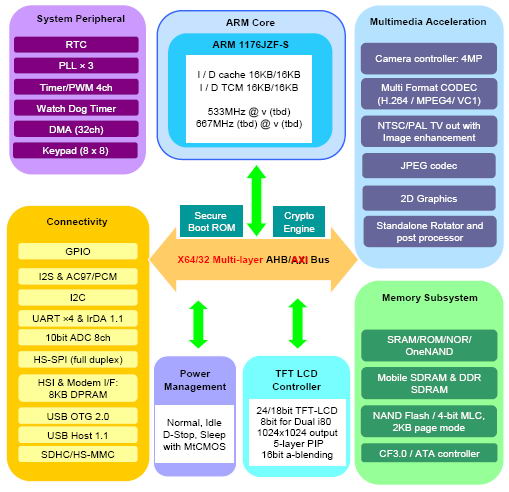

Компания Samsung Semiconductors представила свой первый микроконтроллер на ядре ARM1176 – S3C6400. Новинка работает на частотах 533 и 634МГц, имеет 64/32-битную внутреннюю шину и мощную периферию. Встроенный многоформатный кодек (MFC) обеспечивает кодирование/декодирование MPEG4/H.263, H264 и декодирование VC1. Также поддерживается передачу видео в режиме реального времени и вывод картинки в режиме NTSC и PAL. S3C6400 содержит интерфейсы работы с внешней памятью оптимизированные для подключения любых типов памяти (см. блок-схему). Для уменьшения стоимости системы в целом, микроконтроллер имеет множество полезных аппаратных блоков, таких как: интерфейс для подключения видеокамеры, контроллер TFT, блок управления питанием, CF+, интерфейс ATA, четыре UART, 32 канала DMA и т.д.

В ближайшее время ожидается поступление на склад МТ-Систем первой партии микроконтроллеров S3C6400 с частотой 634МГц (S3C6400X63-YB80). Информацию по отладочной плате SMDK6400, а также софт WinCE 6.0 и Linux можно скачать

здесь.

Характеристики:

ARM Core

· The ARM1176JZF-S processor incorporates ARM V6 architecture. It supports the ARM and Thumb™ instruction sets, and Jazelle technology for direct execution of Java byte codes.

· A range of SIMD DSP instructions that operate on 16-bit or 8-bit data values in 32-bit registers.

· ARM1176JZF Features

o TrustZone™ security extensions•

o S/W Driven Power Management

o High-speed Advanced Microprocessor Bus Architecture (AMBA) Advanced

o Extensible Interface (AXI) level two interfaces supporting prioritized multiprocessor implementations.

o Integer unit with integral Embedded ICE-RT logic

o Eight-stage pipeline

o Branch prediction with return stack

o Low interrupt latency configuration

o External coprocessor interface and coprocessors CP14 and CP15

o Instruction and Data Memory Management Units (MMUs), managed using Micro TLB structures backed by a unified Main TLB

o Instruction and data caches, including a non-blocking data cache with Hit-Under-Miss (HUM)

o Virtually indexed and physically addressed caches

o 64-bit interface to both caches

o DMA

o Vector Floating-Point (VFP) coprocessor support

o External coprocessor support

o Trace support

o JTAG-based debug

Memory Subsystem

· SRAM/ROM/NOR Interface

o x8 or x16 data bus

o Address range support: 26-bits(64MB)

o Support byte and half-word access

· Muxed OneNAND Interface

o x16 data bus

o Support byte and half-word access

· SDRAM Interface

o X16, x32 data bus

o 1.8V interface voltage

o Density support : up to 1Gb

o x16 data bus with 133Mbps/pin data rate

o Mobile SDRAM feature support :DS (Driver Strength Control)TCSR (Temperature Compensated Self-Refresh Control) PASR (Partial Array Self-Refresh Control)

· Mobile DDR Interface

o x16, x32 data bus with 266Mbps/pin double data rate (DDR)

o 1.8Vinterface voltage

o Density support : up to 1Gb

· NAND Flash Memory for boot loader and data storage

o System can be booted from NAND when system initialization begins

o Rest of memory area is used for storing user data

· NAND Interface

o Support industry standard NAND interface

o 1/4-bit hardware ECC circuit

o x8 data bus

Multimedia Acceleration

· Camera Interface

o 8-bit ITU-R601/ITU-R656 format input

o Up to 4M pixel for scaled or 16M pixel for un-scaled resolution

o YCrCb4:2:2 to 4:2:0 down-sampling, down-scaling for MPEG and JPEG

o RGB 24-bit or 16-bit output for preview

o Image windowing and zoom-in function

o Test pattern generation

o Image flip supports Y-mirror, X-mirror, 180’rotation

o H/W Color Space Conversion

o LCD controller direct path supported

o Image effect supported

· Multi Format CODEC (MFC)

o Real-time Video Encoding & decoding of MPEG4/H.263/H.264 and decoding of WMV9

o MPEG4 Up to Simple Profile : 30fps@SD(720x480)

o Supports H.263 Baseline 30fps@SD(720x480)

o H.264 Baseline Profile Level 3.0 : 30fps@SD(720x480)

o VC1 Decoding : 30fps@SD(720x480)

· JPEG Codec

o Compression/decompression up to 65536 x 65536

o Encoding format: YCbCr4:2:2 or YCbCr4:2:0

o Decoding format: YCbCr4:4:4, YCbCr4:2:2, YCbCr4:2:0 or Gray

· Rotator

o Supported image format : YCbCr4:2:2(interleave), YCbCr4:2:0 (non-interleave), RGB565 and RGB888(unpacked)

o Supported rotate degree : 90, 10, 270, flip vertical and flip horizontal

o Supported image size : 2048 x 2048

· 2D Graphic Accelerator

o Primitive drawing engine

· Line/Point drawing

· Bit Block Trasfer(BitBLT)

· Color expansion: Text drawing

o Per-pixel operation (max 2048x2048 resolution)

· 90°/180°/270°/X-flip/Y-flip rotation

· Window clipping

· Rasterization

· 256-level per-pixel alpha blending

· TV(NTSC/PAL) Encoder with Image Enhancer

o Out Video Format : NTSC-M/PAL-B,D,G,H,I Compliant

o Macro vision for anti-taping (Version 7.1.L1)

o Support source format : YCbCr420/422, RGB 16/18/24

o Built in the MIE (Mobile Image Enhancer) Engine

o Black & White Stretch

o Blue Stretch & Flesh-Tone Correction

o Dynamic Horizontal Peaking & LTI

o Black and White Noise Reduction

o Original, Full Size, Wide Size Video-Out

· Video Post Processor

o Video input format conversion

o Video/Graphic scaling up/down or zooming in/out

o Color space conversion from YCbCrto RGB

o Color space conversion from RGB to YCbCr

o Dedicated local interface for display

o Dedicated Scaler for TV Encoder

· Display Controller

o Support 24/18 bit RGB Interface LCD

o Support 8/6 bit RGB Interface

o Support Dual i80 Interface LCD

o 1/2/4/8bpp Palletized or 8/16/24-bpp Non-Palletized Color-TFT support

o 320X240, 640x480 or other display resolutions up to 1024x1024

o Max. 2K x 2K virtual screen size

o Support 5 Window Layer for PIP or OSD

o Real-time overlay plane multiplexing

o Programmable OSD window positioning

o 16-level alpha blending

Security Subsystem

· On-Chip secure boot ROM

o 32KB secure boot ROM for secure boot

· H/W Crypto Accelerator

o Securely integrated AES, DES/3DES, SHA-1/MD5, RNG

· ARM TrustZoneTM

o Enabling enhanced secure platform for separate (secure/non-secure) execution environment for security sensitive

Connectivity

· I2S Bus Interface

o 2-ch IIS-bus for the audio-codec interface with DMA-based operation

o Serial, 8/16-bit per channel data transfers

o Supports IIS, MSB-justified and LSB-justified data format

o 16, 24, 32, 48 fs of bit clock frequency

o 256, 384, 512, 768 fs of codec clock frequency

· PCM Audio I/F

o 16-bit mono audio I/F

o Master mode only

· AC97 Audio I/F

o Independent channels for stereo PCM In, stereo PCM Out, mono MIC In.

o 16-bit stereo(2-channel) audio.

o Variable sampling rate AC97 Codec interface (48KHz and below)

· Modem I/F

o Asynchronous direct and indirect 16-bit SRAM-style interface (support i80 style)

o On-chip 8KB dual-ported SRAM buffer for direct interface

o On-chip Write/Read FIFO (each 288-word) to support indirect burst transfer

· HSI

o MIPI Standard Draft Compliant

o High speed synchronous serial interface

· CF+/ATA controller

o CF+ and Compact Flash Spec 3.0 compatible including ATA6 (except MDMA operation)

· I2C Bus Interface

o 1-ch Multi-Master IIC-Bus

o Serial, 8-bit oriented and bi-directional data transfers can be made at up to 100 Kbit/s in the standard mode

o Up to 400 Kbit/s in the fast mode

· UART

o 4-channel UART with DMA-based or interrupt-based operation

o Supports 5-bit, 6-bit, 7-bit, or 8-bit serial data transmit/receive

o Supports external clock for the UART operation (UCLK)

o Programmable baud rate

o Loop back mode for testing

o Non-integer clock divides in Baud clock generation (BRM)

· IrDA

o IrDA v1.1 support (1.152Mpbs and 4Mpbs)

o SIR(111.5kbps) mode is supported by the UART IrDA 1.0 block

o Internal 64-byte Tx/Rx FIFO

· USB OTG 2.0

o Complies with the USB OTG 2.0

o Supports high speed up to 480Mbps

o On-chip USB transceiver

· USB Host 1.1

o Complies with the USB 1.1

o Supports full speed up to 12Mbps

o On-chip USB transceiver

· HS-MMC/SDIO

o Multimedia Card Protocol version 4.2 compatible (HS-MMC)

o SD/SDIO Memory Card Protocol version SDA spec version 2.0 compatible

o SDHC (SD High Capacity) card support

o DMA based or Interrupt based operation

o 512 Bytes (HS-MMC) and 64 Bytes (MMC) FIFO for Tx/Rx: 128 word FIFO for Tx/Rx

o CE-ATA support

o 3-ch SD/SDIO

o 1-ch HS-MMC & 1x SD/SDIO

· SPI Interface

o 2-ch Serial Peripheral Interface Protocol with full-duplex: up to 50Mbps

o DMA-based or interrupt-based operation

· Keypad

o 8x8 Key Matrix support

o Provides internal de-bounce filter

· A/D Converter and Touch Screen Interface

o 8-ch multiplexed ADC

o Max. 500Ksamples/sec and 10bit resolution

System Peripheral

· Real Time Clock

o Full clock features: sec, min, hour, date, day, week, month, year

o 32.768 KHz operation

o Alarm interrupt

o Time-tick interrupt

· PLL

o Three on-chip PLLs, APLL/ MPLL / EPLL

o APLL dedicates to ARM core

o MPLL generates the system reference clock

o EPLL generates clocks for the audio interface

· Timer with Pulse Width Modulation

o 4-ch 32-bit Timer with PWM

o 1-ch 32-bit internal timer with DMA-based or interrupt-based operation

o Programmable duty cycle, frequency, polarity

o Dead-zone generation

o Support external clock source

· 16-bit Watch Dog Timer

· DMA

o 4 General DMA embedded. 8 channel supported per each DMA so then totally 32 channel is supported Memory to memory, IO to memory, memory to IO, and IO to IO support

o Burst transfer mode to enhance the transfer rate

· Vectored Interrupt Controller

o multiple interrupt request inputs, one for each interrupt source, and one interrupt request output for the processor interrupt request input

o software can mask out particular interrupt requests

o prioritization of interrupt sources for interrupt nesting.

· Power Management

o Clock-off control for individual components

o Various power-down modes are available such as Slow, Idle, Stop and Sleep mode

o Wake-up by one of external interrupts or by the RTC alarm interrupt