Экономически выгодная замена FPGA на ASIC. Быстрая разработка и постановка на производство заказных микросхем от корпорации Toshiba

Фирма МТ-Систем предлагает крупным клиентам интегральные микросхемы, выполненные на заказ (ASIC), на мощностях корпорации Toshiba, в качестве экономически выгодной замены ПЛИС.

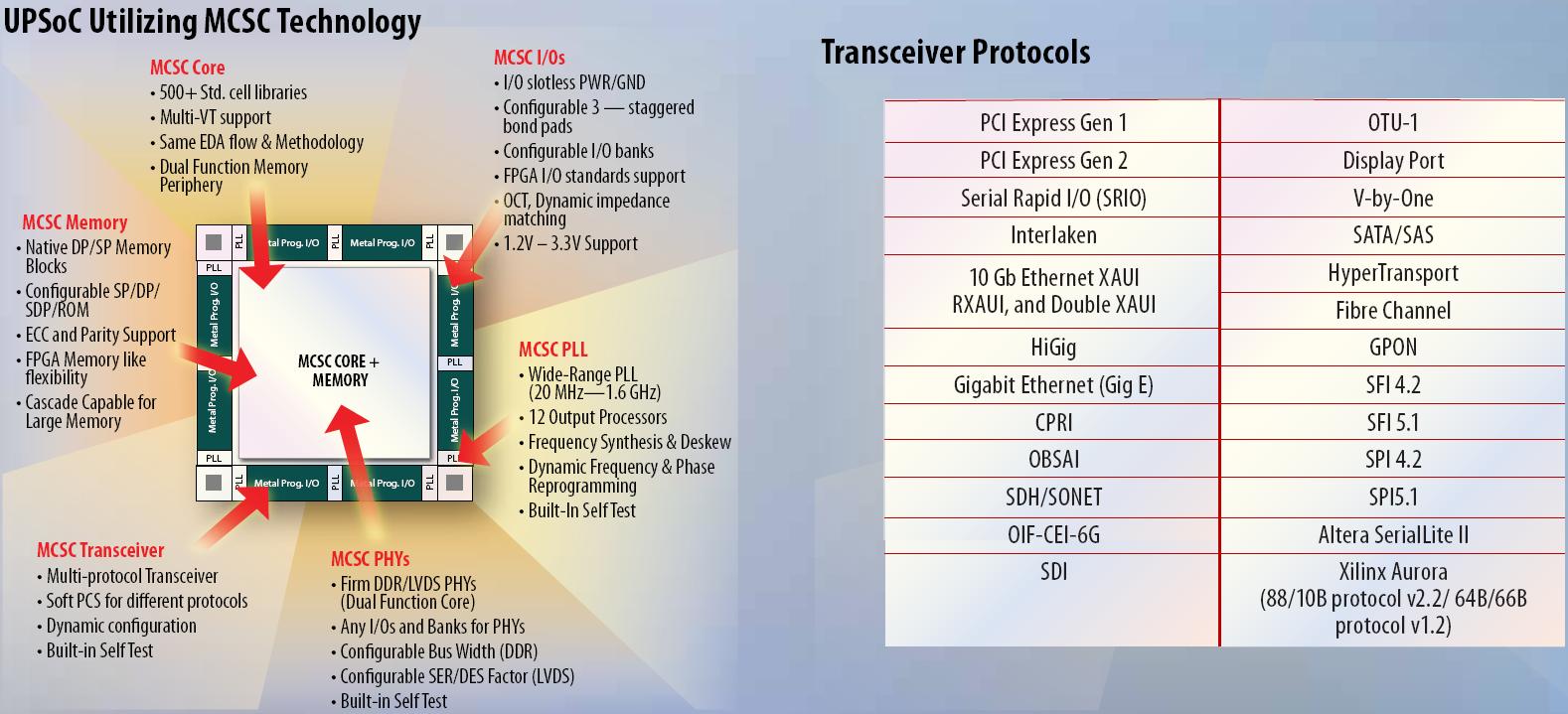

Благодаря запатентованной технологии Fit Fast Structured Arrays (FFSA™ европейское название Ultimate Platform SoC (UPSoC)) заказчик получает следующие технико-экономические преимущества:

- Единовременные затраты на проектирование (NRE) уменьшены в 5 раз в сравнении с технологией разработки на стандартах ячейках (standard cell ASIC).

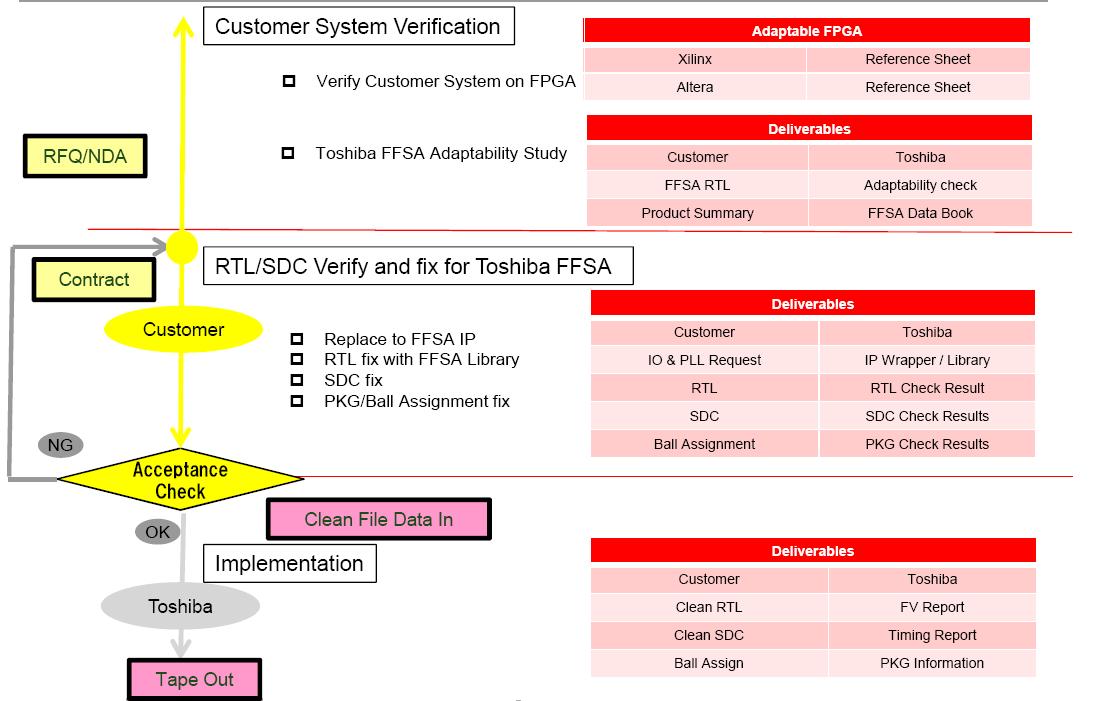

- Ускоренный вывод микросхемы на рынок: до 5 недель из прототипа, описанного на уровне регистровых передач (RTL).

- Уменьшение рисков, благодаря использованию проверенных IP-ядер и методов.

- Простата внесение изменений

- Разработка нескольких ASIC на одной платформе

- Гибкость настройки вводов-выводов на подобии FPGA

- Гибкое конфигурирование памяти (ROM, SP, DP RAMs).

- Поддержка перевода проекта из ПЛИС Altera и Xilinх с сохранением с совместимости по корпусу

- Производительность увеличивается до 5 раз по сравнению с ПЛИС

- Снижение энергопотребления от 8 до 16 раз по сравнению с ПЛИС

Этапы разработки/производства заказной ASIC

В основе технологии FFSA™, обеспечивающей выше приведенные преимущества, лежит использование кристаллов с заранее сформированными блоками, которые конфигурируются с минимальными усилиями, с помощью дополнительных заказных слоев металлизации.

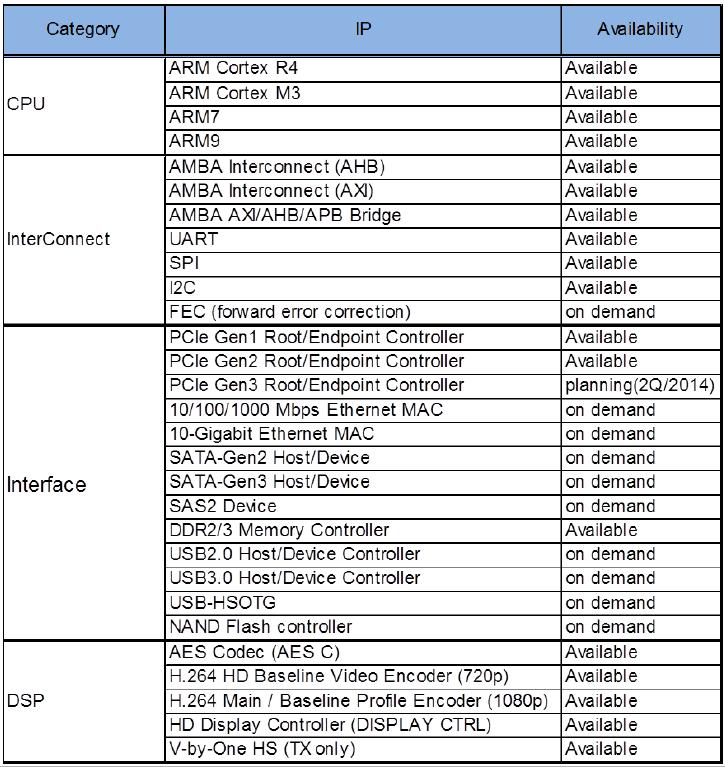

В состав блоков входят массивы вентилей и память. Заказчикам доступны специализированные IP-ядра: процессоров ARM; внутренних шин; интерфейсов и DSP.

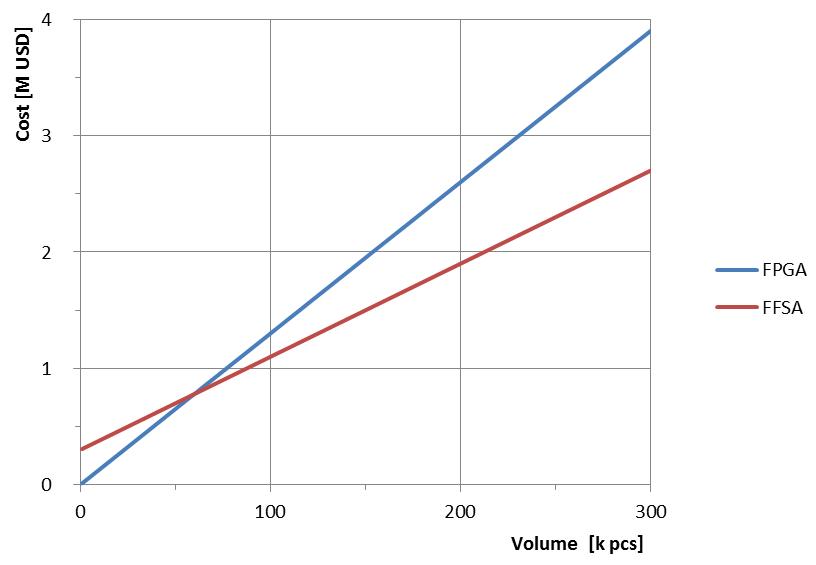

Общая стоимость продукции (TTL), рассчитывается как:

На ПЛИС (FPGA):

TTL = PP * QTY, PP – стоимость заказа микросхемы FPGA.

По технологии FFSA™:

TTL = NRE + SP * QTY, где QTY: количество, SP: стоимость производства.

Например, для продукции из нижнего ценового сегмента рынка (Low End):

|

|

Замена FPGA

|

|

TTL=$13*20*10 =$2.6M |

|

|

FFSA NRE: $0,3M $8*20*10=$1.6M TTL=$0.3M+$1.6M=$1.9M |

|

|

Выгода: $2.6M-$1.9M=$0.7M Экономия: (0.7/2.6)*100=27% |

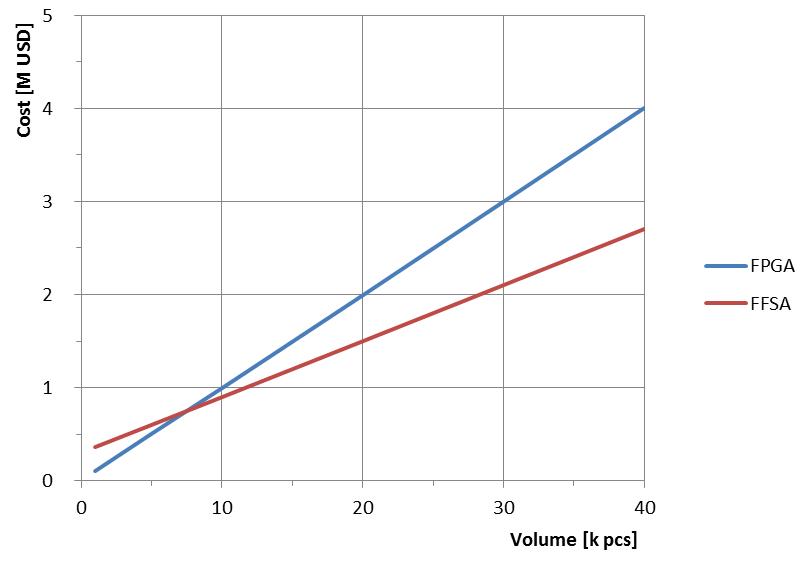

Для продукции из верхнего ценового сегмента рынка (High End):

|

|

Замена FPGA

|

|

TTL=$10*10*5 =$5M |

|

|

FFSA NRE: $0,3M $60*10*5=$3M TTL=$0.3M+$3M=$3.3M |

|

|

Выгода: $5M-$3.3M=$1.7M Экономия: (1.7/5)*100=34% |

Как видно из рисунка порог равнозначной стоимости изделий для High End продукции наступает уже от 6000 изделий за весь жизненный цикл продукции.

За подробной информацией обращайтесь:

toshiba@mt-system.ru

+7 (812) 325-3685 доб.1414