# WT12

DATA SHEET

Tuesday, 17 January 2012

Version 2.95

# Copyright © 2000-2012 Bluegiga Technologies All rights reserved. Bluegiga Technologies assumes no responsibility for any errors which may appear in this manual. Furthermore, Bluegiga Technologies reserves the right to alter the hardware, software, and/or specifications detailed here at any time without notice and does not make any commitment to update the information contained here. Bluegiga's products are not authorized for use as critical components in life support devices or systems. The WRAP is a registered trademark of Bluegiga Technologies

The Bluetooth trademark is owned by the Bluetooth SIG Inc., USA and is licensed to Bluegiga Technologies.

All other trademarks listed herein are owned by their respective owners.

## **Table of Contents**

| 1 | Bloc | ck Diagram and Descriptions                      | 6  |

|---|------|--------------------------------------------------|----|

| 2 | Elec | ctrical Characteristics                          | 8  |

|   | 2.1  | Absolute maximum ratings                         | 8  |

|   | 2.2  | Recommended operating conditions                 | 8  |

|   | 2.3  | Terminal characteristics                         | 8  |

|   | 2.4  | Current consumption                              | 9  |

|   | 2.5  | Radio characteristics and general specifications | 10 |

|   | 2.6  | Radio Characteristics – Basic Data Rate          | 11 |

|   | 2.6. | 1 Transmitter radio characteristics              | 11 |

|   | 2.6. | 2 Receiver radio characteristics                 | 12 |

|   | 2.7  | Radio Characteristics – Enhanced Data Rate       | 14 |

|   | 2.7. | 1 Transmitter radio characteristics              | 14 |

|   | 2.7. | 2 Receiver radio characteristics                 | 15 |

| 3 | WT   | 12 Pin Description                               | 16 |

| 4 | Phy  | sical Interfaces                                 | 19 |

|   | 4.1  | UART Interface                                   | 19 |

|   | 4.1. | 1 UART Configuration While RESET is Active       | 20 |

|   | 4.1. | 2 UART Bypass Mode                               | 20 |

|   | 4.2  | USB Interface                                    | 22 |

|   | 4.2. | 1 USB Pull-Up Resistor                           | 22 |

|   | 4.2. | 2 Self Powered Mode                              | 22 |

|   | 4.2. | 3 Bus Powered Mode                               | 23 |

|   | 4.2. | 4 Suspend Current                                | 23 |

|   | 4.2. | 1 3 3                                            |    |

|   | 4.2. | 6 USB Driver                                     | 24 |

|   | 4.2. | 7 USB 1.1 Compliance                             | 24 |

|   | 4.2. | 8 USB 2.0 Compatibility                          | 24 |

|   | 4.3  | SPI Interface                                    | 25 |

|   | 4.4  | PCM Interface                                    | 26 |

|   | 4.4. |                                                  |    |

|   | 4.4. | 2 Long Frame Sync                                | 27 |

|   | 4.4. | 3 Short Frame Sync                               | 27 |

|   | 4.4. | ·                                                |    |

|   | 4.4. | 5 GCI Interface                                  | 28 |

|   | 4.4. | 6 Slots and Sample Formats                       | 28 |

|   | 4.4. | 7 Additional Features                            | 29 |

|   | 4.4. | 8 PCM Configuration                              | 29 |

| 5 I | I/O Para | allel Ports                                 | 31 |

|-----|----------|---------------------------------------------|----|

| 6   | Softwar  | re Stacks                                   | 32 |

| 6.1 | l iWl    | RAP Stack                                   | 32 |

| 6.2 | 2 HC     | CI Stack                                    | 33 |

| (   | 6.2.1    | Standard functionality                      | 33 |

| (   | 6.2.2    | Extra functionality:                        | 35 |

| 6.3 | 3 VIV    | /I Stack                                    | 36 |

| 6.4 | 4 So     | oftware Development                         | 37 |

| 7 I | Enhand   | ced Data Rate                               | 38 |

| 7.1 | l En     | hanced Data Rate Baseband                   | 38 |

| 7.2 | 2 En     | hanced Data Rate /4 DQPSK                   | 38 |

| 7.3 | 3 8D     | QPSK                                        | 38 |

| 8 I | Layout   | and Soldering Considerations                | 40 |

| 8.1 | l So     | oldering recommendations                    | 40 |

| 8.2 | 2 Lay    | yout guidelines                             | 40 |

| 9 \ | WT12 p   | physical dimensions                         | 43 |

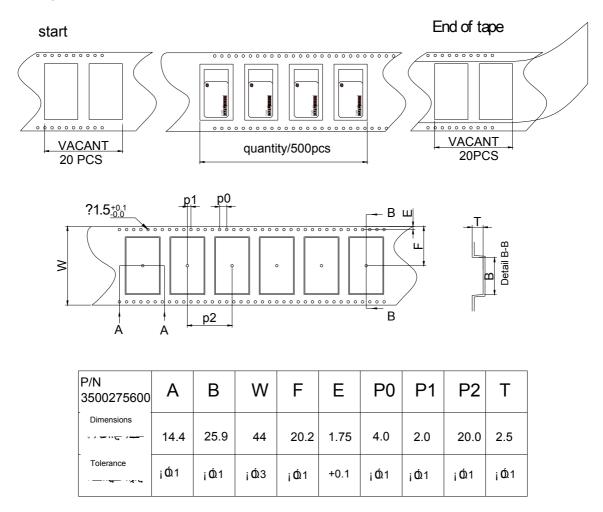

| 10  | Pack     | age                                         | 45 |

| 11  | Certif   | fications                                   | 47 |

| 11  | .1       | Bluetooth                                   | 47 |

| 11  | .2       | FCC and IC                                  | 47 |

| 11  | .3       | CE                                          | 49 |

| 11  | .4       | Japan                                       | 50 |

| 12  | RoHS     | S Statement with a List of Banned Materials | 51 |

| 13  | Conta    | act Information                             | 52 |

## WT12 Bluetooth® module

#### **DESCRIPTION**

WT12 is a next-generation, class 2, *Bluetooth*® 2.1 + *EDR* (Enhanced Data Rates) module. It introduces three times faster data rates compared to existing *Bluetooth*® 1.2 modules even with lower power consumption! WT12 is a highly integrated and sophisticated *Bluetooth*® module, containing all the necessary elements from *Bluetooth*® radio to antenna and a fully implemented protocol stack. Therefore WT12 provides an ideal solution for developers who want to integrate *Bluetooth*® wireless technology into their design with limited knowledge of *Bluetooth*® and RF technologies.

By default WT12 module is equipped with powerful and easy-to-use iWRAP firmware. iWRAP enables users to access *Bluetooth*® functionality with simple ASCII commands delivered to the module over serial interface - it's just like a *Bluetooth*® modem.

#### **APPLICATIONS**

- · Hand held terminals

- · Industrial devices

- · Point-of-Sale systems

- PCs

- · Personal Digital Assistants (PDAs)

- · Computer Accessories

- · Access Points

- · Automotive Diagnostics Units

#### **FEATURES**

- Fully Qualified Bluetooth system v2.1 + EDR, CE and FCC and Japan

- Integrated chip antenna

- Industrial temperature range from -40°C to +85°C

- RoHS Compliant

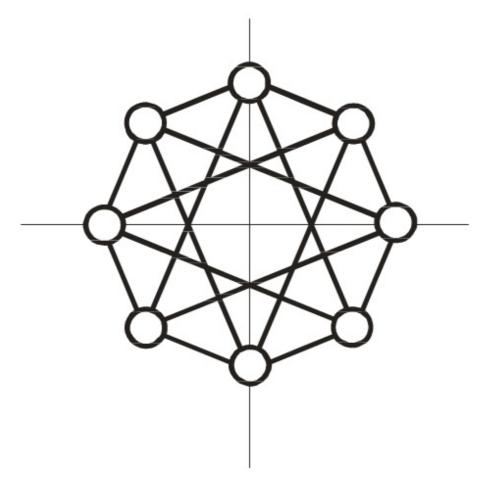

- Full Speed Bluetooth Operation with Full Piconet

- Scatternet Support

- USB version 2.0 compatible

- UART with bypass mode

- Support for 802.11 Coexistence

- 8Mbits of Flash Memory

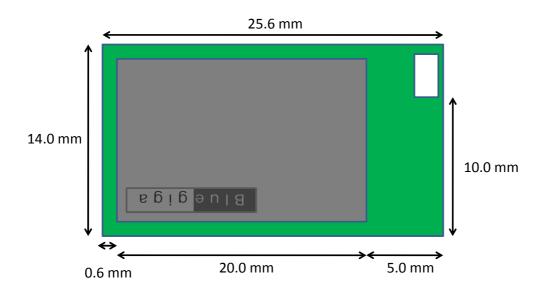

Figure 1: Physical outlook of WT12

#### **ORDERING INFORMATION**

|                           | Internal chip antenna |

|---------------------------|-----------------------|

| iWRAP 3.0 firmware        | WT12-A-AI3            |

| iWRAP 2.2.0 firmware      | WT12-A-AI             |

| HCI firmware, BT2.1 + EDR | WT12-A-HCI21          |

| HCI firmware, BT2.0 + EDR | WT12-A-HCI            |

| Custom firmware           | WT12-A-C (*           |

**Table 1: Ordering information**

To order custom firmware you must have a properly filled <u>Custom Firmware Order From</u> and unique ordering code issued by Bluegiga.

Contact <u>support@bluegiga.com</u> for more information.

<sup>\*)</sup> Custom firmware means any standard firmware with custom parameters (like UART baud rate), custom firmware developer by customer or custom firmware developed by Bluegiga for the customer.

## 1 Block Diagram and Descriptions

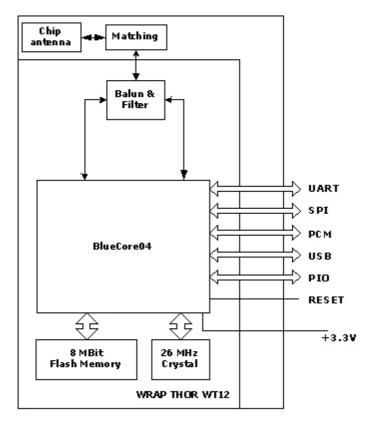

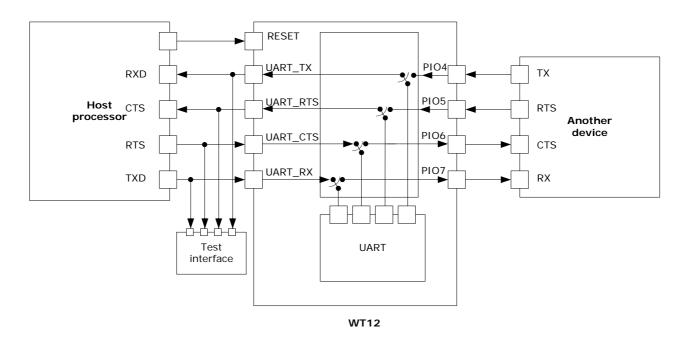

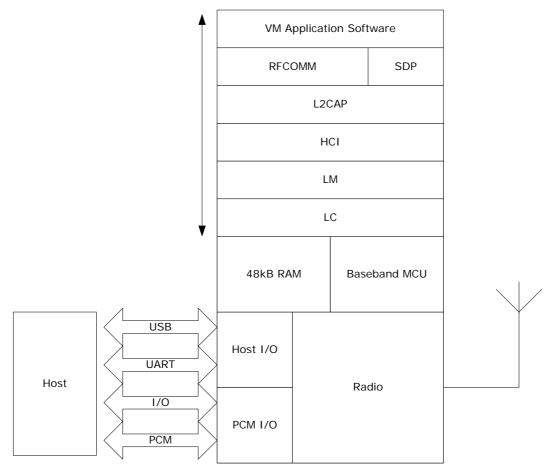

Figure 2: Block Diagram of WT12

## BlueCore04

BlueCore4 is a single chip *Bluetooth* solution which implements the *Bluetooth* radio transceiver and also an on chip microcontroller. BlueCore4 implements *Bluetooth*® 2.1 + EDR (Enhanced Data Rate) and it can deliver data rates up to 3 Mbps.

The microcontroller (MCU) on BlueCore04 acts as interrupt controller and event timer run the *Bluetooth* software stack and control the radio and host interfaces. A 16-bit reduced instruction set computer (RISC) microcontroller is used for low power consumption and efficient use of memory.

BlueCore04 has 48Kbytes of on-chip RAM is provided to support the RISC MCU and is shared between the ring buffers used to hold voice/data for each active connection and the general purpose memory required by the *Bluetooth* stack.

#### Crystal

The crystal oscillates at 26MHz.

#### **Flash**

Flash memory is used for storing the *Bluetooth* protocol stack and Virtual Machine applications. It can also be used as an optional external RAM for memory intensive applications.

#### Balun / filter

Combined balun and filter changes the balanced input/output signal of the module to unbalanced signal of the monopole antenna. The filter is a band pass filter (ISM band).

#### Matching

Antenna matching components match the antenna to 50 Ohms.

#### **Antenna**

The antenna is ACX AT3216 chip antenna.

#### **USB**

This is a full speed Universal Serial Bus (USB) interface for communicating with other compatible digital devices. WT12 acts as a USB peripheral, responding to requests from a Master host controller such as a PC.

#### **Synchronous Serial Interface**

This is a synchronous serial port interface (SPI) for interfacing with other digital devices. The SPI port can be used for system debugging. It can also be used for programming the Flash memory.

#### **UART**

This is a standard Universal Asynchronous Receiver Transmitter (UART) interface for communicating with other serial devices.

#### **Audio PCM Interface**

The audio pulse code modulation (PCM) Interface supports continuous transmission and reception of PCM encoded audio data over *Bluetooth*.

#### Programmable I/O

WT12 has a total of 6 digital programmable I/O terminals. These are controlled by firmware running on the device.

#### Reset

This can be used to reset WT12.

#### 802.11 Coexistence Interface

Dedicated hardware is provided to implement a variety of coexistence schemes. Channel skipping AFH (Adaptive Frequency Hopping), priority signaling, channel signaling and host passing of channel instructions are all supported. The features are configured in firmware. Since the details of some methods are proprietary (e.g. Intel WCS) please contact Bluegiga Technologies for details.

## 2 Electrical Characteristics

## 2.1 Absolute maximum ratings

|                          | Min  | Max       | Unit |

|--------------------------|------|-----------|------|

| Storage temperature      | -40  | 85        | °C   |

| Operating temperature    | -40  | 85        | °C   |

| Supply voltage           | -0,3 | 3,6       | V    |

| Terminal voltages        | -0,4 | Vdd + 0,4 | V    |

| Output current from PIOS |      | 35        | mA   |

The module should not continuously run under these conditions. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability and cause permanent damage to the device.

**Table 2: Absolute maximum ratings**

# 2.2 Recommended operating conditions

|                       | Min                | Max | Unit |

|-----------------------|--------------------|-----|------|

| Operating temperature | -40                | 85  | °C   |

| Supply voltage        | 3,1 <sup>(1)</sup> | 3,6 | V    |

| Terminal voltages     | 0                  | Vdd | V    |

$<sup>^{1)}</sup>$  WT12 operates as low as 2,7 V supply voltage. However, to safely meet the USB specification for minimum voltage for USB data lines, minimum of 3,1 V supply is required.

**Table 3: Recommended operating conditions**

## 2.3 Terminal characteristics

|                                         | Min       | Тур  | Max       | Unit |

|-----------------------------------------|-----------|------|-----------|------|

| I/O voltage levels                      |           |      |           |      |

| V <sub>IL</sub> input logic level low   | -0,4      | -    | 0,8       | V    |

| V <sub>IH</sub> input logic level high  | 0,7Vdd    | -    | Vdd + 0,4 | V    |

| V <sub>OL</sub> output logic level low  | -         | -    | 0,2       | V    |

| V <sub>OH</sub> output logic level high | Vdd - 0,2 | -    | -         | V    |

| Reset terminal                          |           |      |           |      |

| V <sub>TH,res</sub> threshold voltage   | 0,64      | 0,85 | 1,5       | V    |

| R <sub>IRES</sub> input resistance      |           | 220  |           | kΩ   |

| C <sub>IRES</sub> input capacitance     |           | 220  |           | nF   |

| Input and tri-state current with        |           |      |           |      |

| Strong pull-up                          | -100      | -40  | -10       | μΑ   |

| Strong pull-down                        | 10        | 40   | 100       | μΑ   |

| Weak pull-up                            | -5        | -1   | -0,2      | μΑ   |

| Weak pull-down                          | 0,2       | 1    | 5         | μΑ   |

| I/O pad leakage current                 | -1        | 0    | 1         | μΑ   |

| Vdd supply current                      |           |      |           |      |

| TX mode                                 | -         | -    | 70        | mA   |

| RX mode                                 | -         | -    | 70        | mA   |

**Table 4: Terminal characteristics**

# 2.4 Current consumption

Test conditions: Room temperature, Vdd = 3,3 V, iWRAP firmware

| OPERATION MODE                                         | Peak<br>supply<br>current | AVG<br>supply<br>current | Unit | Notes                                                             |

|--------------------------------------------------------|---------------------------|--------------------------|------|-------------------------------------------------------------------|

| Peak current at TX mode                                | 70                        | -                        | mΑ   | -                                                                 |

| Peak current at RX mode                                | 70                        | -                        | mΑ   | -                                                                 |

| IDLE                                                   | -                         | 3                        | mΑ   | Module is idle Default settings                                   |

| IDLE, Deep Sleep ON                                    | -                         | 1,2                      | mΑ   | Module is idle                                                    |

| IDLE, Deep Sleep ON<br>NOT visible, NOT<br>connectable | -                         | 0,056                    | mA   | Module is idle (Minimum consumption),<br>SET BT PAGEMODE 0 2000 1 |

| INQUIRY                                                | -                         | 44,7                     | mA   | Device discovery with INQUIRY command                             |

| NAME                                                   | -                         | 44,7                     | mΑ   | Name resolution                                                   |

| CALL                                                   | -                         | 44,7                     | mA   | CALL [ADDR] 1101 RFCOMM                                           |

| CONNECT<br>Master                                      | -                         | 6,2                      | mA   | No data was transmitted, Default settings                         |

| CONNECT<br>Slave                                       | -                         | 22,4                     | mA   | No data was transmitted, Default settings                         |

| CONNECT + Sniff, Master                                | -                         | 4,7                      | mΑ   | Connected (SET BT SNIFF 40 20 1 8)                                |

| CONNECT + Sniff, Slave                                 | -                         | 4,6                      | mΑ   | Connected (SET BT SNIFF 40 20 1 8)                                |

| CONNECT + sniff, Master                                | -                         | 2,3                      | mA   | No data transmitted<br>(SET BT SNIFF 1000 20 1 8)                 |

| CONNECT + sniff, Slave                                 | -                         | 2,3                      | mA   | No data transmitted<br>(SET BT SNIFF 1000 20 1 8)                 |

| CONNECT + park, Master                                 | -                         | 3,1                      | mΑ   | No data transmittedPark parameter 1000                            |

| CONNECT + park, Slave                                  | -                         | 2,3                      | mΑ   | No data transmittedPark parameter 1000                            |

| DATA, Master                                           | -                         | 31,5                     | mΑ   | Data transmitted @ 115200bps                                      |

| DATA, Slave                                            | -                         | 29,2                     | mΑ   | Data transmitted @ 115200bps                                      |

| DATA + Sniff, Master                                   | -                         | 19,6                     | mA   | Data transmitted @ 115200bps<br>(SET BT SNIFF 40 20 1 8)          |

| DATA + Sniff, Slave                                    | -                         | 22,6                     | mA   | Data transmitted @ 115200bps<br>(SET BT SNIFF 40 20 1 8)          |

| DATA + Sniff, Master                                   | -                         | 3,9                      | mA   | Data transmitted<br>(SET BT SNIFF 1000 20 1 8)                    |

**Table 5: Current consumption**

# 2.5 Radio characteristics and general specifications

|                           |                | Specification                                                                    | Note                     |  |  |

|---------------------------|----------------|----------------------------------------------------------------------------------|--------------------------|--|--|

| Operating frequency range |                | ISM Band                                                                         |                          |  |  |

| Lower quard<br>band       |                | 2 MHz                                                                            |                          |  |  |

| Upper quard<br>band       |                | 3,5 MHz                                                                          |                          |  |  |

| Carrier frequency         |                | 2402 MHz 2480 MHz                                                                | f = 2402 + k,<br>k = 078 |  |  |

| Modulation<br>method      |                | GFSK (1 Mbps)<br>P/4 DQPSK (2Mbps)                                               |                          |  |  |

| Hopping                   |                |                                                                                  |                          |  |  |

|                           | GFSK:          | Asynchronous, 723.2 kbps / 57.6 kbps<br>Synchronous: 433.9 kbps / 433.9 kbps     |                          |  |  |

| Maximum data<br>rate      | P/4<br>DQPSK:  | Asynchronous, 1448.5 kbps / 115.2 kbps<br>Synchronous: 869.7 kbps / 869.7 kbps   |                          |  |  |

|                           | 8DQPSK:        | Asynchronous, 2178.1 kbps / 177.2 kbps<br>Synchronous: 1306.9 kbps / 1306.9 kbps |                          |  |  |

| Receiving signal range    | -82 to -20 dBm |                                                                                  | Typical condition        |  |  |

| Receiver IF frequency     |                | 1.5 MHz                                                                          |                          |  |  |

| Transmission              | Min            | -119 dBm                                                                         |                          |  |  |

| power                     | Max            | +1 +3 dBm                                                                        |                          |  |  |

| RF input impedance        |                |                                                                                  |                          |  |  |

| Compliance                | Blue           |                                                                                  |                          |  |  |

| USB specification         |                |                                                                                  |                          |  |  |

Table 6: Radio characteristics and general specifications

## 2.6 Radio Characteristics - Basic Data Rate

## 2.6.1 Transmitter radio characteristics

WT12 meets the Bluetooth v2.1 + EDR specification between -40 $^{\circ}$ C and +85 $^{\circ}$ C. TX output is guaranteed to be unconditionally stable over the guaranteed temperature range.

Measurement conditions: T = 20°C, Vdd = 3,3V

| Item                                                    | Typical value | Bluetooth specification         | Unit     |

|---------------------------------------------------------|---------------|---------------------------------|----------|

| Maximum output power <sup>1,2</sup>                     | +2.5          | -6 to 4 <sup>3</sup>            | dBm      |

| Variation in RF power over                              |               |                                 |          |

| temperature range with                                  | 1.5           | -                               | dB       |

| compensation enabled <sup>4</sup>                       |               |                                 |          |

| Variation in RF power over                              |               |                                 |          |

| temperature range with                                  | 2.0           | -                               | dB       |

| compensation disabled <sup>4</sup>                      |               |                                 |          |

| RF power control range                                  | 35            | ≥ 16                            | dB       |

| RF power range control                                  | 0.5           | _                               | dB       |

| resolution <sup>5</sup>                                 | 0.0           |                                 | uB       |

| 20dB bandwidth for modulated                            | 780           | ≤ 1000                          | kHz      |

| carrier                                                 | . 66          | = 1000                          | 2        |

| Adjacent channel transmit power                         | -40           | ≤ 20                            | dBm      |

| $F = F_0 \pm 2MHz^{6,7}$                                |               | = -0                            |          |

| Adjacent channel transmit power                         | -45           | ≤ -40                           | dBm      |

| $F = F_0 \pm 3MHz^{6,7}$                                | 70            | <u> </u>                        | авт      |

| Adjacent channel transmit power                         | -50           | < <b>-40</b>                    | dBm      |

| $F = F_0 \pm > 3MHz^{6,7}$                              | -50           | ≥ <del>-4</del> 0               | иын      |

| $\Delta f1_{avg}$ Maximum Modulation                    | 165           | 140 <f1<sub>avg&lt;175</f1<sub> | kHz      |

| $\Delta f2_{max}$ Maximum Modulation                    | 150           | 115                             | kHz      |

| $\Delta$ f1 <sub>avg</sub> / $\Delta$ f2 <sub>avg</sub> | 0.97          | ≥ 0.80                          | -        |

| Initial carrier frequency tolerance                     | 6             | ≤ 75                            | kHz      |

| Drift Rate                                              | 8             | ≤ 20                            | kHz/50μs |

| Drift (single slot packet)                              | 7             | ≤ 25                            | kHz      |

| Drift (five slot packet)                                | 9             | ≤ 40                            | kHz      |

| 2 <sup>nd</sup> Harmonic content                        | -65           | ≤ -30                           | dBm      |

| 3 <sup>rd</sup> Harmonic content                        | -45           | ≤ -30                           | dBm      |

Table 7: Transmitter radio characteristics at basic data rate and temperature 20°C

- 1. WT12 firmware maintains the transmit power to be within the *Bluetooth* v2.1 + EDR specification limits.

- Measurement made using a PSKEY\_LC\_MAX\_TX\_POWER setting corresponds to a PSKEY\_LC\_POWER\_TABLE power table entry of 63.

- 3. Class 2 RF-transmit power range, *Bluetooth* v2.1 + EDR specification.

- To some extent these parameters are dependent on the matching circuit used, and its behavior over temperature. Therefore these parameters may be beyond CSR's direct control.

- 5. Resolution guaranteed over the range -5dB to -25dB relative to maximum power for TX Level >20.

- 6. Measured at F0= 2441MHz.

7. Up to three exceptions are allowed in the *Bluetooth* v2.1 + EDR specification. WT12s guaranteed to meet the ACP performance as specified by the *Bluetooth* v2.1 + EDR specification.

|                               | Frequency (GHz)            | Тур  | Unit    | Cellular band          |

|-------------------------------|----------------------------|------|---------|------------------------|

|                               | $0.869 - 0.894^{1}$        | -145 |         | GSM 850                |

| Emitted power in              | $0.869 - 0.894^2$          | -145 |         | CDMA 850               |

| cellular bands                | $0.925 - 0.960^{1}$        | -145 |         | GSM 900                |

| measured at the               | $1.570 - 1.580^3$          | -145 | dBm/kHz | GPS                    |

| unbalanced port of the balun. | 1.805 – 1.880 <sup>1</sup> | -145 |         | GSM 1800 / DCS<br>1800 |

|                               | 1.930 – 1.990 <sup>4</sup> | -145 |         | PSC 1900               |

| Output power 4dBm             | 1.930 – 1.990 <sup>1</sup> | -145 |         | GSM 1900               |

|                               | $1.930 - 1.990^2$          | -145 |         | CDMA 1900              |

|                               | $2.110 - 2.170^2$          | -142 |         | W-CDMA 2000            |

|                               | $2.110 - 2.170^2$          | -144 |         | W-CDMA 2000            |

Table 8: Transmitter radio characteristics at basic data rate and temperature 20°C

#### Notes:

- 1. Integrated in 200kHz bandwidth and then normalized to a 1Hz bandwidth.

- 2. Integrated in 1.2MHz bandwidth and then normalized to a 1Hz bandwidth.

- 3. Integrated in 1MHz bandwidth. and then normalized to a 1Hz bandwidth.

- 4. Integrated in 30kHz bandwidth and then normalized to a 1Hz bandwidth.

- 5. Integrated in 5MHz bandwidth and then normalized to a 1Hz bandwidth.

## 2.6.2 Receiver radio characteristics

Measurement conditions: T = 20°C, Vdd = 3,3V

|                         | Frequency<br>(GHz) | Тур | Bluetooth specification | Unit |

|-------------------------|--------------------|-----|-------------------------|------|

| Sensitivity at 0.1% BER | 2.402              | -84 |                         |      |

| for all packet types    | 2.441              | -84 | ≤ 75                    | dBm  |

|                         | 2.480              | -84 |                         |      |

| Maximum received sign   | al at 0.1% BER     | 10  | ≥ -20                   | dBm  |

Table 9: Receiver radio characteristics at basic data rate and temperature 20°C

|                                                      | Frequency<br>(GHz)   | Тур | Bluetooth specification | Unit   |

|------------------------------------------------------|----------------------|-----|-------------------------|--------|

| Continuous power required to block                   | 30-2000              | TBD | ≥ -10                   |        |

| Bluetooth reception (for sensitivity of -            | 2000-2400            | TBD | ≥ -27                   | dBm    |

| 67dBm with 0.1% BER) measured at                     | 2500-3000            | TBD | ≥ -27                   | иын    |

| the unbalanced port of the balun.                    | 3000-3300            | TBD | ≥ -27                   |        |

| C/I co-channel                                       |                      | 6   | ≤ 11                    | dB     |

| Adjacent channel selectivity C/I F=F <sub>0</sub> +  | 1MHz <sup>1,2</sup>  | -5  | ≤ 0                     | dB     |

| Adjacent channel selectivity C/I $F=F_0$ -           | 1MHz <sup>1,2</sup>  | -4  | ≤ 0                     | dB     |

| Adjacent channel selectivity C/I F=F <sub>0</sub> +  | 2 MHz <sup>1,2</sup> | -38 | ≤ -30                   | dB     |

| Adjacent channel selectivity C/I $F=F_0$ -           | 2 MHz <sup>1,2</sup> | -23 | ≤ -20                   | dB     |

| Adjacent channel selectivity C/I F=F <sub>0</sub> +  | 3 MHz <sup>1,2</sup> | -45 | ≤ -40                   | dB     |

| Adjacent channel selectivity C/I $F=F_0$ -           | 5 MHz <sup>1,2</sup> | -44 | ≤ -40                   | dB     |

| Adjacent channel selectivity C/I F=F <sub>Imac</sub> | 1,2<br>ie            | -22 | ≤ 9                     | dB     |

| Maximum level of intermodulation inter               | ferers <sup>3</sup>  | -30 | ≥ -39                   | dBm    |

| Spurious output level <sup>4</sup>                   | •                    | TBD | -                       | dBm/Hz |

Table 10: Receiver radio characteristics at basic data rate and temperature 20°C

- 1. Up to five exceptions are allowed in the *Bluetooth* v2.1 + EDR specification. BlueCore4 is guaranteed to meet the C/I performance as specified by the *Bluetooth* v2.1 + EDR specification.

- 2. Measured at F = 2441MHz

- 3. Measured at f1-f2 = 5MHz. Measurement is performed in accordance with *Bluetooth* RF test RCV/CA/05/c. i.e. wanted signal at -64dBm

- 4. Measured at the unbalanced port of the balun. Integrated in 100kHz bandwidth and then normalized to 1Hz. Actual figure is typically below TBD dBm/Hz except for peaks of -52dBm in band at 2.4GHz and d80dBm at 3.2GHz

|                              | Frequency<br>(GHz) | Тур | Unit | Cellular band       |

|------------------------------|--------------------|-----|------|---------------------|

| Emitted power in cellular    | 0.824 - 0.849      | 2.0 |      | GSM 850             |

| bands required to block      | 0.824 - 0.849      | TBD |      | CDMA                |

| Bluetooth reception (for     | 0.880 - 0.915      | 5.0 |      | GSM 900             |

| sensitivity of -67dBm with   | 1.710 – 1.785      | 4.0 | dBm  | GSM 1800 / DCS 1800 |

| 0.1% BER) measured at the    | 1.710 – 1.785      | 3.0 |      | GSM 1900 / PCS 1900 |

| unbalanced port of the       | 1.850 – 1.910      | TBD |      | CDMA 1900           |

| balun.                       | 1.920 – 1.980      | TBD |      | W-CDMA 2000         |

| Continuous power in cellular | 0.824 - 0.849      | -10 |      | GSM 850             |

| bands required to block      | 0.824 - 0.849      | TBD |      | CDMA                |

| Bluetooth reception (for     | 0.880 - 0.915      | -10 |      | GSM 900             |

| sensitivity of-72dBm with    | 1.710 – 1.785      | -9  | dBm  | GSM 1800 / DCS 1800 |

| 0.1% BER) measured at the    | 1.850 – 1.910      | -9  |      | GSM 1900 / PCS 1900 |

| unbalanced port of the       | 1.850 – 1.910      | TBD |      | CDMA 1900           |

| balun.                       | 1.920 – 1.980      | TBD |      | W-CDMA 2000         |

Table 11: Receiver radio characteristics at basic data rate and temperature 20°C

## 2.7 Radio Characteristics - Enhanced Data Rate

## 2.7.1 Transmitter radio characteristics

Measurement conditions: T = 20°C, Vdd = 3,3V

|                                          |           | Тур | Bluetooth specification  | Unit |

|------------------------------------------|-----------|-----|--------------------------|------|

| Maximum output power <sup>1</sup>        |           | +1  | -6 to 4 <sup>2</sup>     | dBm  |

| Relative transmit power <sup>3</sup>     |           | -1  | -4 to 1                  | dB   |

| Carrier frequency stability <sup>3</sup> |           | 3   | ≤ 10                     | kHz  |

| Modulation<br>accuracy <sup>3,4</sup>    | RMS DEV   | ı   | ≤ 13 <sup>5</sup>        | %    |

|                                          | 99% DEV   | 1   | ≤ 20 <sup>5</sup>        | %    |

|                                          | Peak DEVM | -   | ≤ <b>25</b> <sup>5</sup> | %    |

Table 12: Transmitter radio characteristics at enhanced data rate and temperature 20°C

- 1. Results shown are referenced to input of the RF balun.

- 2. WT12 firmware maintains the transmit power to be within the Bluetooth v2.1 + EDR specification limits

- 3. Class 2 RF transmit power range, *Bluetooth* v2.1 + EDR specification

- 4. Measurements methods are in accordance with the EDR RF Test Specification v2.1.E.2

- 5. Modulation accuracy utilizes differential error vector magnitude (DEVM) with tracking of the carrier frequency drift.

- 6. The Bluetooth specification values are for 8DPSK modulation (values for the S/4 DQPSK modulation are less stringent)

## 2.7.2 Receiver radio characteristics

Measurement conditions: T = 20°C, Vdd = 3,3V

|                                         | Modulation | Тур                | Bluetooth specification | Unit |  |

|-----------------------------------------|------------|--------------------|-------------------------|------|--|

| Sensitivity at 0.1% BER for             | П/4 DQPSK  | -87                | ≤ -70                   |      |  |

| all packet types <sup>1</sup>           | 8DQPSK     | -79                | ≤ -70                   | dPm  |  |

| Maximum received signal at              | П/4 DQPSK  | -7                 | ≥ -20                   | dBm  |  |

| 0.1% BER <sup>1</sup>                   | 8DQPSK     | -7                 | ≥ -20                   |      |  |

| C/I co-channel at 0.1% BER <sup>1</sup> | П/4 DQPSK  | +11                | ≤ 13                    |      |  |

|                                         | 8DQPSK     | +19                | ≤ 21                    |      |  |

| Adjacent channel selectivity            | П/4 DQPSK  | -8                 | ≤ 0                     |      |  |

| $C/I F = F_0 + 1MHz^{1,2,3}$            | 8DQPSK     | -2                 | ≤ 5                     |      |  |

| Adjacent channel selectivity            | П/4 DQPSK  | -8                 | ≤ 0                     |      |  |

| $C/I F = F_0 - 1MHz^{1,2,3}$            | 8DQPSK     | -2                 | ≤ 5                     |      |  |

| Adjacent channel selectivity            | П/4 DQPSK  | -35                | ≤ -30                   |      |  |

| $C/I F = F_0 + 2MHz^{1,2,3}$            | 8DQPSK     | -35                | ≤ -25                   | dB   |  |

| Adjacent channel selectivity            | П/4 DQPSK  | -23                | ≤ -20                   | ив   |  |

| $C/I F = F_0 - 2MHz^{1,2,3}$            | 8DQPSK     | -19                | ≤ -13                   |      |  |

| Adjacent channel selectivity            | П/4 DQPSK  | □/4 DQPSK -43 ≤-40 |                         |      |  |

| $C/I F = F_0 + 3MHz^{1,2,3}$            |            |                    | ≤ -33                   |      |  |

| Adjacent channel selectivity            | П/4 DQPSK  | -43                | ≤ -40                   |      |  |

| $C/I F = F_0 - 5MHz^{1,2,3}$            | 8DQPSK     | -38                | ≤ -33                   |      |  |

| Adjacent channel selectivity            | П/4 DQPSK  | -17                | ≤ -7                    |      |  |

| $C/I F = F_{Image}^{1,2,3}$             | 8DQPSK     | -11                | ≤ 0                     |      |  |

Table 13: Receiver radio characteristics at enhanced data rate and temperature 20°C

- 1. Results shown are referenced to input of the RF balun

- 2. Measurements methods are in accordance with the EDR RF Test Specification v2.1.E.2

- 3. Up to five exceptions are allowed in EDR RF Test Specification v2.1.E.2. WT12 is guaranteed to meet the C/I performance as specified by the EDR RF Test Specification v2.1.E.2.

- 4. Measured at F0 = 2405MHz, 2441MHz, 2477MHz

## 3 WT12 Pin Description

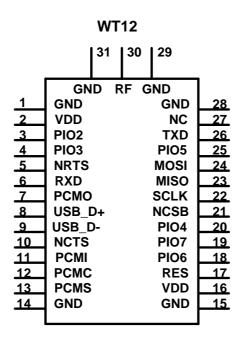

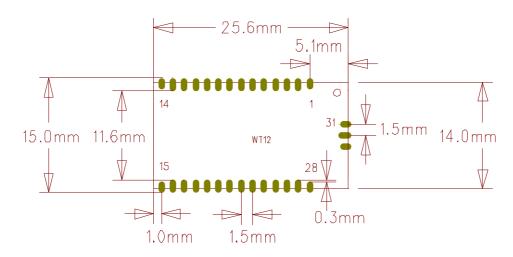

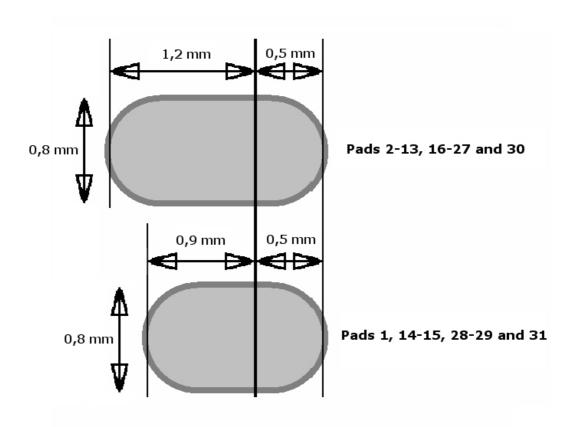

Figure 3: WT12 connection diagram

#### GND (pins 1, 14, 15, 28, 29 and 31)

Connect GND pins to the ground plane of PCB.

#### **VDD** (pins 2 and 16)

3.3 V supply voltage connection. WT12 has an internal decoupling capacitor and LC filter to block high frequency disturbances. Thus external filtering is usually not needed. It is however recommended to leave an option for an external high Q 10pF decoupling capacitor in case EMC problems arise.

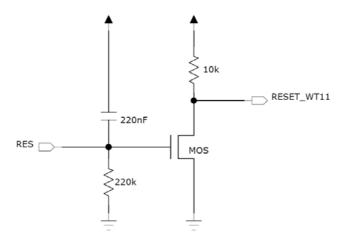

#### **RES (pin 17)**

The RESET pin is an active high reset and is internally filtered using the internal low frequency clock oscillator. A reset will be performed between 1.5 and 4.0ms following RESET being active. It is recommended that RESET be applied for a period greater than 5ms.

WT12 has an internal reset circuitry, which keeps reset pin active until supply voltage has reached stability in the start up. This ensures that supply for the flash memory inside the WT12 will reach stability before BC4 chip fetches instructions from it. Schematic of the reset circuitry is shown in figure 4. Rising supply voltage charges the capacitor, which will activate the reset of WT12. The capacitor discharges through 220 k $\Omega$  resistor, which eventually deactivates the reset. Time constant of the RC circuitry is set such that the supply voltage is safely stabilized before reset deactivates. Pull-up or pull-down resistor should not be connected to the reset pin to ensure proper star up of WT12.

Figure 4: WT12 internal reset circuitry

#### PIO2 - PIO7 (pins 3, 4, 18, 19, 20 and 25)

Programmable digital I/O lines. All PIO lines can be configured through software to have either weak or strong pull-ups or pull-downs. Configuration for each PIO line depends on the application. See section 10 "I/O parallel ports" for detailed descriptions for each terminal. Default configuration for all of the PIO lines is input with weak internal pull-up.

#### NC (pin 27)

This pin is internally connected to PIO1.

#### NRTS (pin 5)

CMOS output with weak internal pull-up. Can be used to implement RS232 hardware flow control where RTS (request to send) is active low indicator. UART interface requires external RS232 transceiver chip.

#### NCTS (pin 10)

CMOS input with weak internal pull-down. Can be used to implement RS232 hardware flow control where CTS (clear to send) is active low indicator. UART interface requires external RS232 transceiver chip.

#### RXD (pin 6)

CMOS input with weak internal pull-down. RXD is used to implement UART data transfer from another device to WT12. UART interface requires external RS232 transceiver chip.

#### **TXD (pin 26)**

CMOS output with weak internal pull-up. TXD is used to implement UART data transfer from WT12 to another device. UART interface requires external RS232 transceiver chip.

#### PCMO (pin 7)

CMOS output with weak internal pull-down. Used in PCM (pulse code modulation) interface to transmit digitized audio.

#### PCMI (pin 11)

CMOS input with weak internal pull-down. Used in PCM interface to receive digitized audio.

## PCMC (pin 12)

Bi-directional synchronous data clock signal pin with weak internal pull-down. PCMC is used in PCM interface to transmit or receive CLK signal. When configured as a master, WT12 generates clock signal for the PCM interface. When configured as a slave PCMC is an input and receives the clock signal from another device.

## PCMS (pin 13)

Bi-directional synchronous data strobe with weak internal pull-down. When configured as a master, WT12 generates SYNC signal for the PCM interface. When configured as a slave PCMS is an input and receives the SYNC signal from another device.

#### USB D+ (pin 8)

Bi-directional USB data line with a selectable internal 1.5 k $\Omega$  pull-up implemented as a current source (compliant with USB specification v1.2) External series resistor is required to match the connection to the characteristic impedance of the USB cable.

#### USB\_D- (pin 9)

Bi-directional USB data line. External series resistor is required to match the connection to the characteristic impedance of the USB cable.

#### NCSB (pin 21)

CMOS input with weak internal pull-up. Active low chip select for SPI (serial peripheral interface).

#### SCLK (pin 22)

CMOS input for the SPI clock signal with weak internal pull-down. WT12 is the slave and receives the clock signal from the device operating as a master.

#### MISO (pin 23)

SPI data output with weak internal pull-down.

#### MOSI (pin 24)

SPI data input with weak internal pull-down.

#### **RF (pin 30)**

Connect external RF-transceiver antenna to this pin when chip antenna is not in use.

# 4 Physical Interfaces

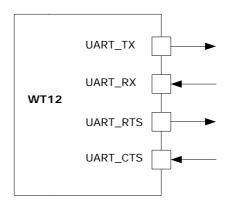

#### 4.1 UART Interface

WT12 Universal Asynchronous Receiver Transmitter (UART) interface provides a simple mechanism for communicating with other serial devices using the RS232 standard. The UART interface of WT12 uses voltage levels of 0 to Vdd and thus external transceiver IC is required to meet the voltage level specifications of UART.

Figure 5: WT12 UART interface

Four signals are used to implement the UART function, as shown in Figure 6. When WT12 is connected to another digital device, UART\_RX and UART\_TX transfer data between the two devices. The remaining two signals, UART\_CTS and UART\_RTS, can be used to implement RS232 hardware flow control where both are active low indicators. DTR, DSR and DCD signals can be implemented using PIO terminals of WT12. All UART connections are implemented using CMOS technology and have signaling levels of 0V and VDD.

In order to communicate with the UART at its maximum data rate using a standard PC, an accelerated serial port adapter card is required for the PC.

| Parameter           |         | Possible values      |  |

|---------------------|---------|----------------------|--|

| Baud<br>rate        | Minimum | 1200 baud (≤2%Error) |  |

|                     |         | 9600 baud (≤1%Error) |  |

|                     | Maximum | 3.0Mbaud (≤1%Error)  |  |

| Flow control        |         | RTS/CTS, none        |  |

| Parity              |         | None, Odd, Even      |  |

| Number of stop bits |         | 1 or 2               |  |

| Bits per channel    |         | 8                    |  |

**Table 14: Possible UART settings**

The UART interface is capable of resetting WT12 upon reception of a break signal. A Break is identified by a continuous logic low (0V) on the UART\_RX terminal, as shown in Figure 7. If  $t_{\text{BRK}}$  is longer than the value, defined by the PS Key PSKEY\_HOST\_IO\_UART\_RESET\_TIMEOUT, (0x1a4), a reset will occur. This feature allows a host to initialize the system to a known state. Also, WT12 can emit a Break character that may be used to wake the Host.

Since UART\_RX terminal includes weak internal pull-down, it can't be left open unless disabling UART interface using PS\_KEY settings. If UART is not disabled, a pull-up resistor has to be connected to UART\_RX. UART interface requires external RS232 transceiver, which usually includes the required pull-up.

Figure 6: Break signal

#### Note:

Table 15 shows a list of commonly used Baud rates and their associated values for the Persistent Store Key PSKEY\_UART\_BAUD\_RATE (0x204). There is no requirement to use these standard values. Any Baud rate within the supported range can be set in the Persistent Store Key according to the formula in Equation below.

Baud Rate =

$$\frac{PSKEY\_UART\_BAUD\_RATE}{0.004096}$$

Figure 7: Baud rate calculation formula

| Baud rate | Persistent | Error |        |

|-----------|------------|-------|--------|

|           | Hex        | Dec   | Error  |

| 1200      | 0x0005     | 5     | 1.73%  |

| 2400      | 0x000a     | 10    | 1.73%  |

| 4800      | 0x0014     | 20    | 1.73%  |

| 9600      | 0x0027     | 39    | -0.82% |

| 19200     | 0x004f     | 79    | 0.45%  |

| 38400     | 0x009d     | 157   | -0.18% |

| 57600     | 0x00ec     | 263   | 0.03%  |

| 76800     | 0x013b     | 315   | 0.14%  |

| 115200    | 0x01d8     | 472   | 0.03%  |

| 230400    | 0x03b0     | 944   | 0.03%  |

| 460800    | 0x075f     | 1887  | -0.02% |

| 921600    | 0x0ebf     | 3775  | 0.00%  |

| 1382400   | 0x161e     | 5662  | -0.01% |

| 1843200   | 0x1d7e     | 7550  | 0.00%  |

| 2765800   | 0x2c3d     | 11325 | 0.00%  |

Table 15: UART baud rates and error values

## 4.1.1 UART Configuration While RESET is Active

The UART interface for WT12 while the chip is being held in reset is tri-state. This will allow the user to daisy chain devices onto the physical UART bus. The constraint on this method is that any devices connected to this bus must tri-state when WT12reset is de-asserted and the firmware begins to run.

## 4.1.2 UART Bypass Mode

Alternatively, for devices that do not tri-state the UART bus, the UART bypass mode on WT12 can be used. The default state of WT12 after reset is de-asserted, this is for the host UART bus to be connected to the WT12 UART, thereby allowing communication to WT12 via the UART.

In order to apply the UART bypass mode, a BCCMD command will be issued to WT12 upon this, it will switch the bypass to PIO[7:4] as shown in Figure 9. Once the bypass mode has been invoked, WT12 will enter the deep sleep state indefinitely.

In order to re-establish communication with WT12, the chip must be reset so that the default configuration takes affect.

It is important for the host to ensure a clean *Bluetooth* disconnection of any active links before the bypass mode is invoked. Therefore it is not possible to have active *Bluetooth* links while operating the bypass mode.

The current consumption for a device in UART Bypass Mode is equal to the values quoted for a device in standby mode.

Figure 8: UART bypass mode

#### 4.2 USB Interface

WT12 USB devices contain a full speed (12Mbits/s) USB interface that is capable of driving a USB cable directly. No external USB transceiver is required. To match the connection to the characteristic impedance of the USB cable, series resistors must be included to both of the signal lines. These should be of 1% tolerance and the value required may vary between 0 and 20 ohm with 10 ohm being nominal. The resistors should be placed close to the USB pins of the module in order to avoid reflections. The module has internally 22 ohm resistors in series. The total input impedance seen by the cable is affected by the IC characteristics, track layout and the connector. The cable impedance is approximately 40 ohm.

The device operates as a USB peripheral, responding to requests from a master host controller such as a PC. Both the OHCI and the UHCI standards are supported. The set of USB endpoints implemented can behave as specified in the USB section of the *Bluetooth* v2.1 + EDR specification or alternatively can appear as a set of endpoint appropriate to USB audio devices such as speakers.

As USB is a Master/Slave oriented system (in common with other USB peripherals), WT12 only supports USB Slave operation.

## 4.2.1 USB Pull-Up Resistor

WT12 features an internal USB pull-up resistor. This pulls the USB\_DP pin weakly high when WT12 is ready to enumerate. It signals to the PC that it is a full speed (12Mbit/s) USB device.

The USB internal pull-up is implemented as a current source, and is compliant with Section 7.1.5 of the USB specification v1.2. The internal pull-up pulls USB\_D+ high to at least 2.8V when loaded with a  $15k\Omega$  +/-5% pull-down resistor (in the hub/host). This presents a Therein resistance to the host of at least  $900\Omega$ . Alternatively, an external  $1.5k\Omega$  pull-up resistor can be placed between a PIO line and D+ on the USB cable. The firmware must be alerted to which mode is used by setting PS Key PSKEY\_USB\_PIO\_PULLUP appropriately. The default setting uses the internal pull-up resistor.

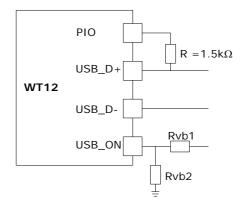

#### 4.2.2 Self Powered Mode

In self powered mode, the circuit is powered from its own power supply and not from the VBUS (5V) line of the USB cable. It draws only a small leakage current (below 0.5mA) from VBUS on the USB cable. This is the easier mode for which to design for, as the design is not limited by the power that can be drawn from the USB hub or root port. However, it requires that VBUS be connected to WT12 via a voltage devider (Rvb1 and Rvb2), so WT12 can detect when VBUS is powered up. Voltage divider is essential to drop the 5V voltage at the VBUS to 3,3V expected at the USB interface of WT12. WT12 will not pull USB DP high when VBUS is off.

Self powered USB designs (powered from a battery or PSU) must ensure that a PIO line is allocated for USB pull-up purposes. A 1.5K 5% pull-up resistor between USB\_DP and the selected PIO line should be fitted to the design. Failure to fit this resistor may result in the design failing to be USB compliant in self powered mode. The internal pull-up in WT12 is only suitable for bus powered USB devices i.e. dongles.

Figure 9: USB in self powered mode

The terminal marked USB\_ON can be any free PIO pin. The PIO pin selected must be registered by setting PSKEY\_USB\_PIO\_VBUS to the corresponding pin number. In self powered mode PSKEY USB PIO PULLUP must be set to match with the PIO selected.

Note:

USB\_ON is shared with WT12 PIO terminals (PIO2-PIO7).

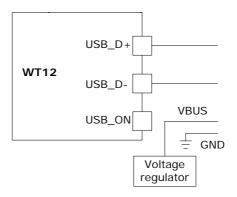

#### 4.2.3 Bus Powered Mode

In bus powered mode the application circuit draws its current from the 5V VBUS supply on the USB cable. WT12 negotiates with the PC during the USB enumeration stage about how much current it is allowed to consume.

For WT12 *Bluetooth* applications, it is recommended that the regulator used to derive 3.3V from VBUS is rated at 100mA average current and should be able to handle peaks of 120mA without fold back or limiting. In bus powered mode, WT12 requests 100mA during enumeration.

When selecting a regulator, be aware that VBUS may go as low as 4.4V. The inrush current (when charging reservoir and supply decoupling capacitors) is limited by the USB specification (see USB specification v1.1, Section 7.2.4.1). Some applications may require soft start circuitry to limit inrush current if more than 10pF is present between VBUS and GND.

The 5V VBUS line emerging from a PC is often electrically noisy. As well as regulation down to 3.3V, applications should include careful filtering of the 5V line to attenuate noise that is above the voltage regulator bandwidth.

In bus powered mode PSKEY\_USB\_PIO\_PULLUP must be set to 16 for internal pull-up (default configuration in WT12).

Figure 10: USB in bus powered mode

## 4.2.4 Suspend Current

All USB devices must permit the USB controller to place them in a USB Suspend mode. While in USB Suspend, bus powered devices must not draw more than 0.5mA from USB VBUS (self powered devices may draw more than 0.5mA from their own supply). This current draw requirement prevents operation of the radio by bus powered devices during USB Suspend.

The voltage regulator circuit itself should draw only a small quiescent current (typically less than 100uA) to ensure adherence to the suspend current requirement of the USB specification. This is not normally a problem with modern regulators. Ensure that external LEDs and/or amplifiers can be turned off by WT12. The entire circuit must be able to enter the suspend mode. (For more details on USB Suspend, see separate CSR documentation).

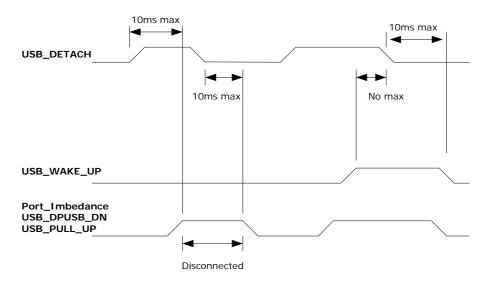

## 4.2.5 Detach and Wake-Up Signaling

WT12 can provide out-of-band signaling to a host controller by using the control lines called 'USB\_DETACH' and 'USB\_WAKE\_UP'. These are outside the USB specification (no wires exist for them inside the USB cable), but can be useful when embedding WT12 into a circuit where no external USB is visible to the user. Both control lines are shared with PIO pins and can be assigned to any PIO

pin by setting the PS Keys PSKEY\_USB\_PIO\_DETACH and PSKEY\_USB\_PIO\_WAKEUP to the selected PIO number.

USB\_DETACH is an input which, when asserted high, causes WT12 to put USB\_D- and USB\_D+ in high impedance state and turned off the pull-up resistor on D+. This detaches the device from the bus and is logically equivalent to unplugging the device. When USB\_DETACH is taken low, WT12 will connect back to USB and await enumeration by the USB host.

USB\_WAKE\_UP is an active high output (used only when USB\_DETACH is active) to wake up the host and allow USB communication to recommence. It replaces the function of the software USB WAKE\_UP message (which runs over the USB cable), and cannot be sent while WT12 is effectively disconnected from the bus.

Figure 11: USB\_DETACH and USB\_WAKE\_UP Signal

## 4.2.6 USB Driver

A USB *Bluetooth* device driver is required to provide a software interface between WT12 and *Bluetooth* software running on the host computer. Suitable drivers are available from <a href="https://www.bluegiga.com/techforum/">www.bluegiga.com/techforum/</a>.

#### 4.2.7 USB 1.1 Compliance

WT12 is qualified to the USB specification v1.1, details of which are available from <a href="http://www.usb.org">http://www.usb.org</a>. The specification contains valuable information on aspects such as PCB track impedance, supply inrush current and product labeling.

Although WT12 meets the USB specification, Bluegiga Technologies cannot guarantee that an application circuit designed around the module is USB compliant. The choice of application circuit, component choice and PCB layout all affect USB signal quality and electrical characteristics. The information in this document is intended as a guide and should be read in association with the USB specification, with particular attention being given to Chapter 7. Independent USB qualification must be sought before an application is deemed USB compliant and can bear the USB logo. Such qualification can be obtained from a USB plug fest or from an independent USB test house.

Terminals USB\_D+ and USB\_D- adhere to the USB specification 2.0 (Chapter 7) electrical requirements.

#### 4.2.8 USB 2.0 Compatibility

WT12 is compatible with USB v2.0 host controllers; under these circumstances the two ends agree the mutually acceptable rate of 12Mbits/s according to the USB v2.0 specification.

## 4.3 SPI Interface

The synchronous serial port interface (SPI) is for interfacing with other digital devices. The SPI port can be used for system debugging. It can also be used for programming the Flash memory. SPI interface is connected using the MOSI, MISO, CSB and CLK pins.

The module operates as a slave and thus MISO is an output of the module. MISO is not in high-impedance state when CSB is pulled high. Instead, the module outputs 0 if the processor is running and 1 if it is stopped. Thus WT11 should not be connected in a multi-slave arrangement by simple parallel connection of slave MISO lines.

#### 4.4 PCM Interface

Pulse Code Modulation (PCM) is a standard method used to digitize audio (particularly voice) patterns for transmission over digital communication channels. Through its PCM interface, WT12 has hardware support for continual transmission and reception of PCM data, thus reducing processor overhead for wireless headset applications. WT12 offers a bi directional digital audio interface that routes directly into the baseband layer of the on chip firmware. It does not pass through the HCl protocol layer.

Hardware on WT12 allows the data to be sent to and received from a SCO connection. Up to three SCO connections can be supported by the PCM interface at any one time.

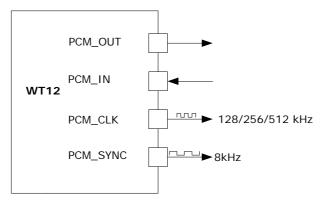

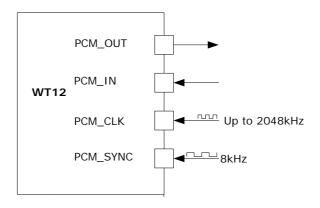

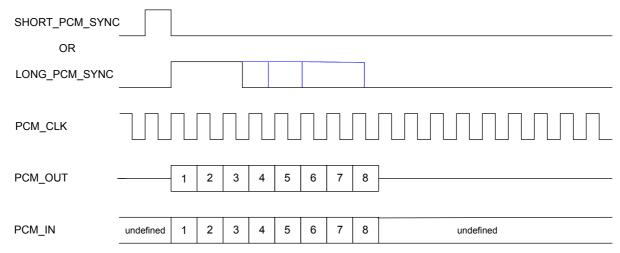

WT12 can operate as the PCM interface Master generating an output clock of 128, 256 or 512kHz. When configured as PCM interface slave it can operate with an input clock up to 2048kHz. WT12 is compatible with a variety of clock formats, including Long Frame Sync, Short Frame Sync and GCI timing environments.

It supports 13 or 16-bit linear, 8-bit  $\mu$ -law or A-law companded sample formats at 8ksamples/s and can receive and transmit on any selection of three of the first four slots following PCM\_SYNC. The PCM configuration options are enabled by setting the PS Key PS KEY\_PCM\_CONFIG32 (0x1b3). WT12 interfaces directly to PCM audio devices including the following:

- Qualcomm MSM 3000 series and MSM 5000 series CDMA baseband devices

- OKI MSM7705 four channel A-law and μ-law CODEC

- Motorola MC145481 8-bit A-law and μ-law CODEC

- Motorola MC145483 13-bit linear CODEC

- STW 5093 and 5094 14-bit linear CODECs

- BlueCore4-External is also compatible with the Motorola SSI™ interface

#### 4.4.1 PCM Interface Master/Slave

When configured as the Master of the PCM interface, WT12 generates PCM CLK and PCM SYNC.

Figure 12: WT12 as PCM master

When configured as the Slave of the PCM interface, WT12 accepts PCM\_CLK and PCM\_SYNC. PCM\_CLK rates up to 2048kHz are accepted.

Figure 13: WT12 as PCM slave

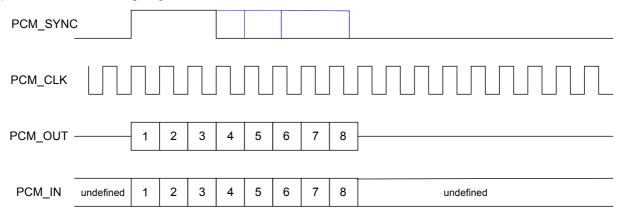

## 4.4.2 Long Frame Sync

Long Frame Sync is the name given to a clocking format that controls the transfer of PCM data words or samples. In Long Frame Sync, the rising edge of PCM\_SYNC indicates the start of the PCM word. When WT12 is configured as PCM Master, generating PCM\_SYNC and PCM\_CLK, then PCM\_SYNC is 8-bits long. When BlueCore4-External is configured as PCM Slave, PCM\_SYNC may be from two consecutive falling edges of PCM\_CLK to half the PCM\_SYNC rate, i.e.  $62.5\mu s$  long.

WT12 samples PCM\_IN on the falling edge of PCM\_CLK and transmits PCM\_OUT on the rising edge. PCM\_OUT may be configured to be high impedance on the falling edge of PCM\_CLK in the LSB position or on the rising edge.

Figure 14: Long frame sync (shown with 8-bit Companded Sample)

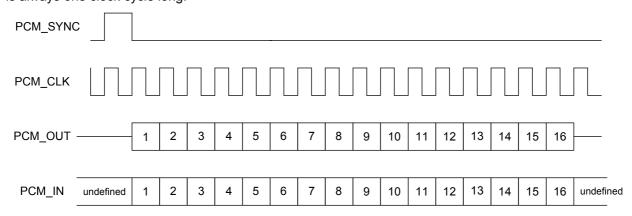

## 4.4.3 Short Frame Sync

In Short Frame Sync the falling edge of PCM\_SYNC indicates the start of the PCM word. PCM\_SYNC is always one clock cycle long.

Figure 15: Short frame sync (shown with 16-bit Companded Sample)

As with Long Frame Sync, WT12 samples PCM\_IN on the falling edge of PCM\_CLK and transmits PCM\_OUT on the rising edge. PCM\_OUT may be configured to be high impedance on the falling edge of PCM\_CLK in the LSB position or on the rising edge.

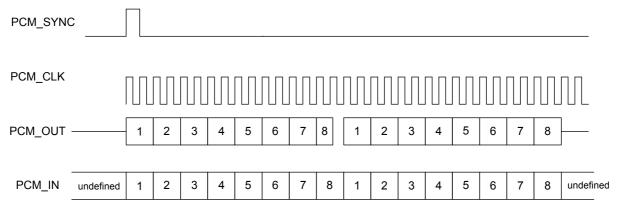

## 4.4.4 Multi Slot Operation

More than one SCO connection over the PCM interface is supported using multiple slots. Up to three SCO connections can be carried over any of the first four slots.

Figure 16: Multi Slot Operation with Two Slots and 8-bit Companded Samples

#### 4.4.5 GCI Interface

WT12 is compatible with the General Circuit Interface, a standard synchronous 2B+D ISDN timing interface. The two 64Kbps B channels can be accessed when this mode is configured.

Figure 17: GCI Interface

The start of frame is indicated by the rising edge of PCM\_SYNC and runs at 8kHz. With WT12 in Slave mode, the frequency of PCM\_CLK can be up to 4.096MHz.

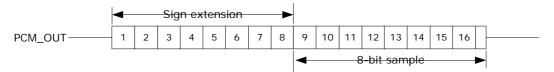

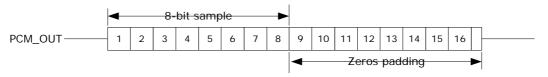

## 4.4.6 Slots and Sample Formats

WT12 can receive and transmit on any selection of the first four slots following each sync pulse. Slot durations can be either 8 or 16 clock cycles. Duration's of 8 clock cycles may only be used with 8-bit sample formats. Durations of 16 clocks may be used with 8, 13 or 16-bit sample formats.

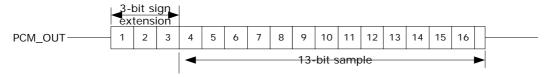

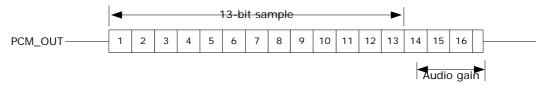

WT12 supports 13-bit linear, 16-bit linear and 8-bit  $\mu$ -law or A-law sample formats. The sample rate is 8ksamples/s. The bit order may be little or big Endian. When 16-bit slots are used, the 3 or 8 unused bits in each slot may be filled with sign extension, padded with zeros or a programmable 3-bit audio attenuation compatible with some Motorola CODECs.

Figure 18: 16-bit slot with 8-bit companded sample and sign extension selected

Figure 19: 16-bit slot with 8-bit companded sample and zeros padding selected

Figure 20: 16-bit slot with 13-bit linear sample and sign extension selected

Figure 21: 16-bit slot with 13-bit linear sample and audio gain selected

### 4.4.7 Additional Features

WT12 has a mute facility that forces PCM\_OUT to be 0. In Master mode, PCM\_SYNC may also be forced to 0 while keeping PCM\_CLK running which some CODECS use to control power down.

## 4.4.8 PCM Configuration

The PCM configuration is set using two PS Keys, PSKEY\_PCM\_CONFIG32 and PSKEY\_PCM\_LOW\_JITTER\_CONFIG. The following tables detail these PS Keys. The default for PSKEY\_PCM\_CONFIG32 key is 0x008000000 i.e. first slot following sync is active, 13-bit linear voice format, long frame sync and interface master generating 256kHz PCM\_CLK from 4MHz internal clock with no tri-stating of PCM\_OUT. PSKEY\_PCM\_LOW\_JITTER\_CONFIG is described in Table 17.

| Name                          | Bit position | Description                                                                                                                                                                                                                                                             |  |

|-------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| -                             | 0            | Set to 0                                                                                                                                                                                                                                                                |  |

| SLAVE MODE EN                 | 1            | 0 selects Master mode with internal generation of PCM_CLK and PCM_SYNC. 1 selects Slave mode requiring externally generated PCM_CLK and PCM_SYNC. This should be set to 1 if 48M_PCM_CLK_GEN_EN (bit 11) is set.                                                        |  |

| SHORT SYNC EN                 | 2            | 0 selects long frame sync (rising edge indicates start of frame), 1 selects short frame sync (falling edge indicates start of frame).                                                                                                                                   |  |

| -                             | 3            | Set to 0                                                                                                                                                                                                                                                                |  |

| SIGN EXTENDED<br>EN           | 4            | 0 selects padding of 8 or 13-bit voice sample into a 16- bit slot by inserting extra LSBs, 1 selects sign extension. When padding is selected with 3-bit voice sample, the 3 padding bits are the audio gain setting; with 8-bit samples the 8 padding bits are zeroes. |  |

| LSB FIRST EN                  | 5            | 0 transmits and receives voice samples MSB first, 1 uses LSB first.                                                                                                                                                                                                     |  |

| TX TRISTATE EN                | 6            | 0 drives PCM_OUT continuously, 1 tri-states PCM_OUT immediately after the falling edge of PCM_CLK in the last bit of an active slot, assuming the next slot is not active.                                                                                              |  |

| TX TRISTATE<br>RISING EDGE EN | 7            | 0 tristates PCM_OUT immediately after the falling edge of PCM_CLK in the last bit of an active slot, assuming the next slot is also not active.  1 tristates PCM_OUT after the rising edge of PCM_CLK.                                                                  |  |

| SYNC SUPPRESS<br>EN           | 8            | 0 enables PCM_SYNC output when master, 1 suppresses PCM_SYNC whilst keeping PCM_CLK running. Some CODECS utilize this to enter a low power state.                                                                                                                       |  |

| GCI MODE EN                   | 9            | 1 enables GCI mode.                                                                                                                                                                                                                                                     |  |

| MUTE EN                       | 10           | 1 forces PCM_OUT to 0.                                                                                                                                                                                                                                                  |  |

| 48M PCM CLK GEN<br>EN         | 11           | 0 sets PCM_CLK and PCM_SYNC generation via DDS from internal 4 MHz clock, as for BlueCore4-External. 1 sets PCM_CLK and PCM_SYNC generation via DDS from internal 48 MHz clock.                                                                                         |  |

| LONG LENGTH<br>SYNC EN        | 12           | 0 sets PCM_SYNC length to 8 PCM_CLK cycles and 1 sets length to 16 PCM_CLK cycles. Only applies for long frame sync and with 48M_PCM_CLK_GEN_EN set to 1.                                                                                                               |  |

| -                             | [20:16]      | Set to 0b00000.                                                                                                                                                                                                                                                         |  |

| MASTER CLK RATE               | [22:21]      | Selects 128 (0b01), 256 (0b00), 512 (0b10) kHz PCM_CLK frequency when master and 48M_PCM_CLK_GEN_EN (bit 11) is low.                                                                                                                                                    |  |

| ACTIVE SLOT                   | [26:23]      | Default is 0001. Ignored by firmaware                                                                                                                                                                                                                                   |  |

| SAMPLE_FORMAT                 | [28:27]      | Selects between 13 (0b00), 16 (0b01), 8 (0b10) bit sample with 16 cycle slot duration 8 (0b11) bit sample 8 cycle slot duration.                                                                                                                                        |  |

Table 16: PSKEY\_PCM\_CONFIG32 description

| Name       | Bit position | Description                                 |  |  |

|------------|--------------|---------------------------------------------|--|--|

| CNT LIMIT  | [12:0]       | Sets PCM_CLK counter limit                  |  |  |

| CNT RATE   | [23:16]      | Sets PCM_CLK count rate.                    |  |  |

| SYNC LIMIT | [31:24]      | Sets PCM_SYNC division relative to PCM_CLK. |  |  |

Table 17: PSKEY\_PCM\_LOW\_JITTER\_CONFIG Description

## 5 I/O Parallel Ports

The Parallel Input Output (PIO) Port is a general-purpose I/O interface to WT12. The port consists of six programmable, bi-directional I/O lines, PIO[2:7]. Programmable I/O lines can be accessed either via an embedded application running on WT12 or via private channel or manufacturer-specific HCl commands.

All PIO lines are configured as inputs with weak pull downs at reset.

#### PIO[2] / USB\_PULL\_UP (1)

The function depends on whether WT12 is a USB or UART capable version. On UART versions, this terminal is a programmable I/O. On USB versions, it can drive a pull-up resistor on USB\_D+. For application using external RAM this terminal may be programmed for chip select.

#### PIO[3] / USB\_WAKE\_UP (1)

On UART versions of WT12 this terminal is a programmable I/O. On USB versions, its function is selected by setting the Persistent Store Key PSKEY\_USB\_PIO\_WAKEUP (0x2cf) either as a programmable I/O or as a USB\_WAKE\_UP function.

#### PIO[4] / USB\_ON (1)

On UART versions of WT12 this terminal is a programmable I/O. On USB versions, the USB\_ON function is also selectable.

#### PIO[5] / USB\_DETACH (1)

On UART versions of WT12 this terminal is a programmable I/O. On USB versions, the USB\_DETACH function is also selectable.

#### PIO[6] / CLK\_REQ

Function is determined by Persistent Store Keys. Using PSKEY\_CLOCK\_REQUEST\_ENABLE, (0x246) this terminal can be configured to be low when WT12 is in deep sleep and high when a clock is required. The clock must be supplied within 4ms of the rising edge of PIO[6] to avoid losing timing accuracy in certain *Bluetooth* operating modes.

#### PIO[7]

Programmable I/O terminal.

## 6 Software Stacks

WT12 is supplied with *Bluetooth* v2.1 + EDR compliant stack firmware, which runs on the internal RISC microcontroller.

The WT12 software architecture allows *Bluetooth* processing and the application program to be shared in different ways between the internal RISC microcontroller and an external host processor (if any). The upper layers of the *Bluetooth* stack (above HCI) can be run either on-chip or on the host processor.

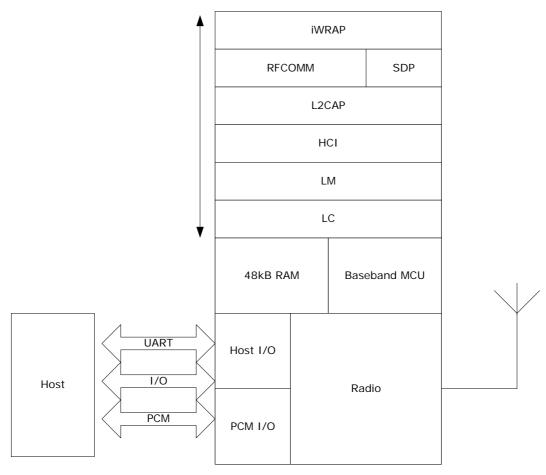

#### 6.1 iWRAP Stack

Figure 22: WRAP THOR VM Stack

In figure 23 above, the iWRAP software solution is described. In this version of the stack firmware shown no host processor is required to run the *Bluetooth* protocol stack. All software layers, including application software, run on the internal RISC processor in a protected user software execution environment known as a Virtual Machine (VM).

The host processor interfaces to iWRAP software via one or more of the physical interfaces, which are also shown in the figure 23. The most common interfacing is done via UART interface using the ASCII commands supported by the iWRAP software. With these ASCII commands the user can access *Bluetooth* functionality without paying any attention to the complexity, which lies in the *Bluetooth* protocol stack.

The user may write applications code to run on the host processor to control iWRAP software with ASCII commands and to develop *Bluetooth* powered applications.

More details of iWRAP software and it's features can be found from *iWRAP User Guide* which can be downloaded from <a href="https://www.bluegiga.com">www.bluegiga.com</a>.

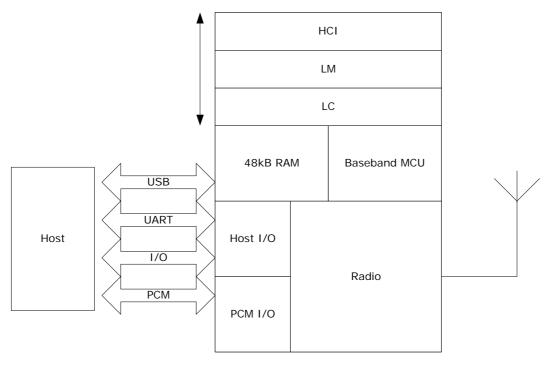

#### 6.2 HCI Stack

Figure 23: HCI Stack

In the implementation shown in figure 24 the internal processor runs the *Bluetooth* stack up to the Host Controller Interface (HCI). The Host processor must provide all upper layers including the application.

## 6.2.1 Standard functionality

The firmware was written against the *Bluetooth* v2.1 + EDR specification and supports the following functionality:

- Secure simple pairing

- Sniff subrating

- Encryption pause resume

- Packet boundary flags

- · Extended inquiry response

- AFH as Master and Automatic Channel Classification

- Faster connection enhanced inquiry scan (immediate FHS response)

- LMP improvements

- Parameter ranges

- Fast Connect Interlaced Inquiry and Page Scan plus RSSI during Inquiry

- SCO handle

- Bluetooth components:

- Baseband (including LC)

- LM

- HCI

- Standard UART and USB HCI Transport Layers

- All standard Bluetooth radio packet types

- Full Bluetooth data rate, enhanced data rates of 2 and 3Mbps. This is the maximum allowed by

- Operation with up to seven active ACL links

- Scatternet v2.5 operation

- eSCO

- Operation with up to three SCO or eSCO links routed to one or more remote devices (dependent on the parameters requested by the host, for example, to have three HV3 SCO links, all the links must go to slave devices)

- All standard SCO voice coding including transparent SCO

- Standard operating modes: Page, Inquiry, Page-Scan and Inquiry-Scan

- All standard pairing, authentication, link key and encryption operations

- Standard Bluetooth power saving mechanisms: Hold, Sniff and Park modes, including Forced Hold

- Dynamic control of peers' transmit power via LMP

- Master/Slave switch

- Broadcast

- Channel quality driven data rate

- All standard Bluetooth test modes

- EDR

## 6.2.2 Extra functionality:

The release extends the standard *Bluetooth* functionality with the following features:

- Support for BCSP, a proprietary, reliable alternative to the standard Bluetooth UART Host Transport (H4)

- o A set of manufacturer-specific HCI extension commands, called BCCMDs, which provide:

- o Access to the IC's general-purpose PIO port

- o Negotiated effective encryption key length on established Bluetooth links

- o Access to the firmware's random number generator

- o Controls to set the default and maximum transmit powers; helping to reduce interference between overlapping, fixed-location piconets

- UART configuration

- Radio transmitter enable/disable; using a simple command to connect to a dedicated hardware switch that determines whether the radio can transmit

- Control of audio routing

- The firmware can read the voltage on several of the IC's external pins. This is normally used to build a

battery monitor, using either VM or host code (BlueCore4-Audio Flash can also read the battery

voltage internally).

- The firmware provides support using VM to control the on-chip Battery Charger hardware for those Ics that provide this functionality

- A block of BCCMDs provides access to the IC's PS configuration database. The database holds the

device's Bluetooth address, Class of Device, radio (transmit class) configuration, SCO routing, LM

and USB constants, etc.

- A UART break condition can be used in three ways:

- o Presenting a UART break condition to the IC can force the IC to perform a hardware reboot

- o Presenting a break condition at boot time can hold the IC in a low power state, preventing normal initialisation while the condition exists

- o With BCSP, the firmware can be configured to assert a break condition to the host before sending data; normally used to wake the host from a Deep Sleep state

- The DFU v1.0 standard has been extended with public/private key authentication, allowing manufacturers to control the firmware that can be loaded onto their *Bluetooth* modules

- A modified version of the DFU v1.0 protocol allows firmware upgrade via the IC's UART

- A block of "radio test" or BIST commands allows direct control of the IC's radio. This aids the

development of modules' radio designs, and can be used to support Bluetooth qualification.

- The firmware provides the VM environment in which to run application-specific code. Although the VM is mainly used with BlueLab, the VM can be used with this build, configured to act as an HCI device, to perform simple tasks such as flashing LEDs via the IC's PIO port.

- Hardware low power modes: Shallow Sleep and Deep Sleep. The IC drops into modes that significantly reduce power consumption when the software goes idle.

- Support for eSCO connections at both HCI and RFCOMM levels

- SCO and eSCO channels are normally routed over HCI (over BCSP). However, up to three SCO/eSCO channels can be routed over the IC's single PCM port (at the same time as routing any other SCO/eSCO channels over HCI). One SCO/eSCO link can be routed over the internal codec.

## 6.3 VM Stack

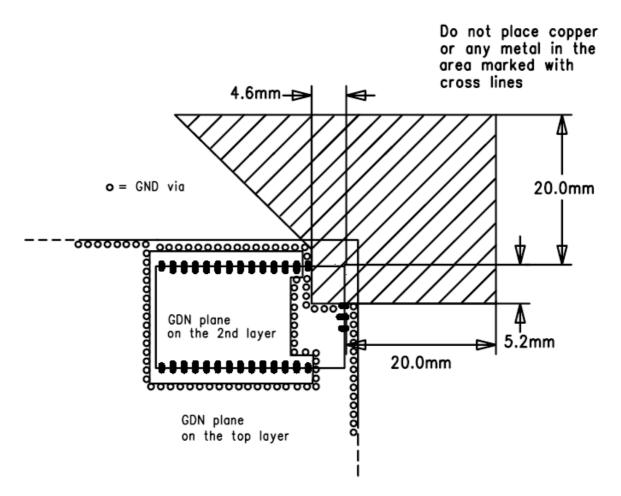

Figure 24: VM Stack

In figure above, this version of the stack firmware shown requires no host processor (but can use a host processor for debugging etc.). All software layers, including application software, run on the internal RISC processor in a protected user software execution environment known as a Virtual Machine (VM).