## **UZ2400**

# Low Power 2.4 GHz Transceiver for IEEE 802.15.4 Standard

**Datasheet**

DS-2400-02

Version: 1.3

The content of this technical document is subject to change without notice. Please contact UBEC for further information.

Released Date: 2008/08/28

All rights are strictly reserved. Any portion of this document shall not be reproduced, copied, or transformed to any other forms without prior permission from Uniband Electronic Corp.

This page is left blank intentionally.

### **UZ2400**

Low Power 2.4 GHz Transceiver for IEEE 802.15.4 Standard

## **Applications**

- ☐ Automated meter reading (AMR)

- ☐ Home/Building/Factory automations

- 2-way low data rate applications

- Wireless sensor network

- PC peripherals

- ☐ Low power wireless communications

- Consumer electronics

## **Introduction**

The UZ2400 is a solution that complies with the IEEE 802.15.4/ZigBee specifications. It integrates a wireless RF transceiver operating at 2.4 GHz with 802.15.4 compliant baseband and MAC layer function blocks. UZ2400 can be combined with a microprocessor (e.g. 8051) for low data rate applications such as home automation, consumer electronics, PC peripherals, toys, industrial automation, etc. The RF block of UZ2400 integrates receiver, transmitter, VCO and PLL within a single IC. It uses advanced radio architecture to minimize the external component count and the power consumption. UZ2400 MAC/Baseband provides the hardware architecture for both the 802.15.4 MAC and the PHY layers. It mainly consists of TX/RX FIFOs, CSMA-CA controller, Superframe constructor, receiving frame filter, security engine and digital signal processing module. The UZ2400 is fabricated with advanced 0.18μm CMOS process and is sealed in a 40-pin QFN 6x6 mm² package.

## **Features**

#### RF/Analog

- ☐ ISM band 2.405~2.480 GHz operation

- ☐ Complete IEEE 802.15.4-2003 specification compliance

- -95 dBm sensitivity and 5 dBm maximum input

- 0 dBm typical output power and 36 dB TX power control range

- ☐ Differential RF input/output and integrated TX/RX switch

- ☐ Integrated low phase noise VCO, frequency

- synthesizer and PLL loop filter

- ☐ Integrated 20 MHz and 32.768KHz oscillator drive.

- ☐ Integrated 100kHz internal oscillator circuit

- ☐ Digital VCO and filter calibration

- ☐ Integrated RSSI ADC and I/Q DACs

- □ Integrated LDO

- ☐ High receiver and RSSI dynamic range

- Support power saving modes

- ☐ Low current consumption, 18 mA in RX and 22

|    | mA in TX mode                                         | 0.18 μm CMOS technology                     |

|----|-------------------------------------------------------|---------------------------------------------|

|    | 2 uA deep sleep mode                                  | Low external component count                |

|    | Small 40-pin leadless QFN 6x6 mm <sup>2</sup> package | 625kbps turbo mode supported                |

|    |                                                       |                                             |

| MA | C/Baseband                                            |                                             |

|    | Complete IEEE 802.15.4-2003 specification             | Hardware security engine(AES-128) with CTR, |

|    | compliance                                            | CCM and CBC-MAC modes                       |

|    | Hardware CSMA-CA mechanism, automatic                 | Four low power operation modes              |

|    | ACK response and FCS check                            | Support all CCA modes and RSSI/LQI          |

|    | Programmable Superframe construction                  | Simple four-wire SPI interface              |

|    | Independent beacon, transmit and GTS FIFO             | I <sup>2</sup> C slave supported            |

|    |                                                       |                                             |

## **Block Diagram**

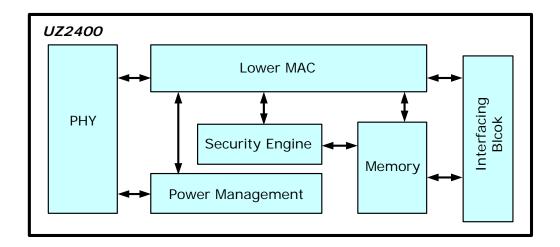

Figure 1 shows the block diagram of UZ2400. UZ2400 is composed of six blocks:

| PHY block       | Security engine block  |

|-----------------|------------------------|

| Lower MAC block | Power management block |

| Memory block    | Interfacing block      |

Detailed descriptions for each block will be described in UZ2400 datasheet.

Figure 1 UZ2400 block diagram

## **Table of Content**

| Applications                                       | 3  |

|----------------------------------------------------|----|

| Introduction                                       | 3  |

| Features                                           | 3  |

| Block Diagram                                      | 4  |

| 1. Pin Configuration                               | 10 |

| 1.1. Device Pin Assignments                        | 10 |

| 1.2. Device Pin Descriptions                       | 11 |

| 2. Electrical Characteristics                      | 13 |

| 2.1. Absolute Maximum Ratings                      |    |

| 2.2. Recommended Operating Conditions              | 13 |

| 2.3. DC Electrical Characteristics                 | 13 |

| 2.4. Radio Frequency AC Characteristics            | 14 |

| 2.4.1. Receiver Radio Frequency AC Characteristics | 14 |

| 2.4.2. Transmitter Radio Frequency Characteristics | 14 |

| 2.5. ESD Notice                                    | 14 |

| 2.6. Peripheral Characteristics                    | 15 |

| 2.7. Power-on and Reset Characteristics            | 15 |

| 2.8. Crystal Parameter Specifications              |    |

| 3. Functional Description                          | 16 |

| 3.1. PHY Block                                     |    |

| 3.1.1. IEEE 802.15.4-2003 PHY Introduction         | 17 |

| 3.1.2. RSSI/ED and LQI                             |    |

| 3.1.3. CCA                                         | 17 |

| 3.2. Lower MAC Block                               | 18 |

| 3.2.1. IEEE 802.15.4-2003 MAC Introduction         | 18 |

| 3.2.2. MAC Timer                                   |    |

| 3.2.3. RXMAC                                       | 22 |

| 3.2.4. TXMAC                                       | 23 |

| 3.2.5. CSMA-CA                                     | 24 |

| 3.3. Memory Block                                  |    |

| 3.3.1. Registers                                   | 28 |

| 3.3.2. FIFOs                                       |    |

| 3.4. Power Management Block                        |    |

| 3.4.1. Power Supply Scheme                         |    |

| 3.4.2. Voltage Regulator                           |    |

| 3.4.3. Battery Monitor                             | 30 |

| 3.4.4. Power-on Reset                              | 30 |

| 3.4.5. Power Modes                                 | 30 |

| 3.4.6. Counters for Power Saving Modes             |    |

| 3.4.7. Hardware Acknowledgement                    | 35 |

| 3.5. Security Engine Block                         |    |

| 3.6. Analog Circuits                               | 38 |

|        | 3.6.1. Crystal Oscillators                                     | 38 |

|--------|----------------------------------------------------------------|----|

|        | 3.6.2. PLL Frequency Synthesizer                               | 39 |

|        | 3.6.3. Internal 100kHz Sleep Clock Oscillator for Sleep Clock  | 39 |

|        | 3.6.4. 32.768 kHz Crystal Oscillator for Sleep Clock           | 39 |

| 3.     | .7. Peripherals                                                | 39 |

|        | 3.7.1. SPI Interface                                           | 39 |

|        | 3.7.2. I <sup>2</sup> C Interface                              | 43 |

|        | 3.7.3. GPIO                                                    | 45 |

|        | 3.7.4. Interrupt Signal                                        | 46 |

| 4. App | olication Guide                                                | 48 |

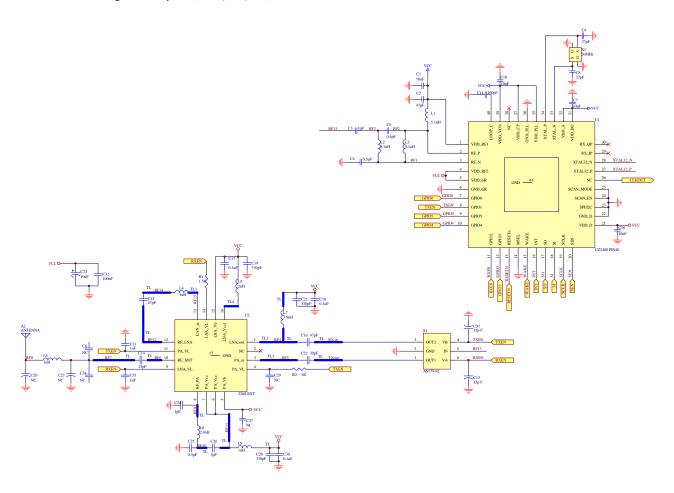

| 4.     | .1. Hardware Connection                                        |    |

|        | 4.1.1. Typical Application Connection Using SPI Interface      |    |

|        | 4.1.2. Adding External Power Amplifier and Low Noise Amplifier |    |

| 4.     | .2. Registers and FIFOs                                        |    |

|        | 4.2.1. Memory Space                                            |    |

|        | 4.2.2. Register Summary                                        |    |

|        | 4.2.3. Security Buffers                                        |    |

|        | 4.2.4. Initialization                                          |    |

|        | 4.2.5. Interrupt Configuration                                 |    |

|        | 4.2.6. External Power Amplifier Configuration                  |    |

|        | 4.2.7. Turbo Mode Configuration                                |    |

| 4.     | .3. Typical TX Operations                                      |    |

|        | 4.3.1. Transmit Packet in Normal FIFO                          |    |

|        | 4.3.2. Transmit Packet in GTS FIFO                             |    |

|        | 4.3.3. Transmit Packet in Beacon FIFO                          |    |

|        | 4.3.4. Transmit Packet with Security Encryption                |    |

| 4.     | .4. Typical RX Operations                                      |    |

|        | 4.4.1. Receive Packet in RXFIFO                                |    |

|        | 4.4.2. Receive Packet with Security Decryption                 |    |

| 4.     | .5. Beacon Mode Operations                                     |    |

|        | 4.5.1. Beacon Mode Setting                                     |    |

|        | 4.5.2. Beacon Mode GTS Setting                                 |    |

| 4.     | .6. Power Saving Mode Operations                               |    |

|        | 4.6.1. Power Saving for Non-beacon-enabled Mode                |    |

|        | 4.6.2. Power Saving for Beacon-enabled Mode                    |    |

|        | 4.6.3. External Wake-up Mode                                   |    |

|        | .7. Battery Monitor Operations                                 |    |

| 4.     | .8. Upper Cipher Encryption and Decryption Operations          |    |

|        | 4.8.1. Upper Cipher Encryption                                 |    |

|        | 4.8.2. Upper Cipher Decryption                                 |    |

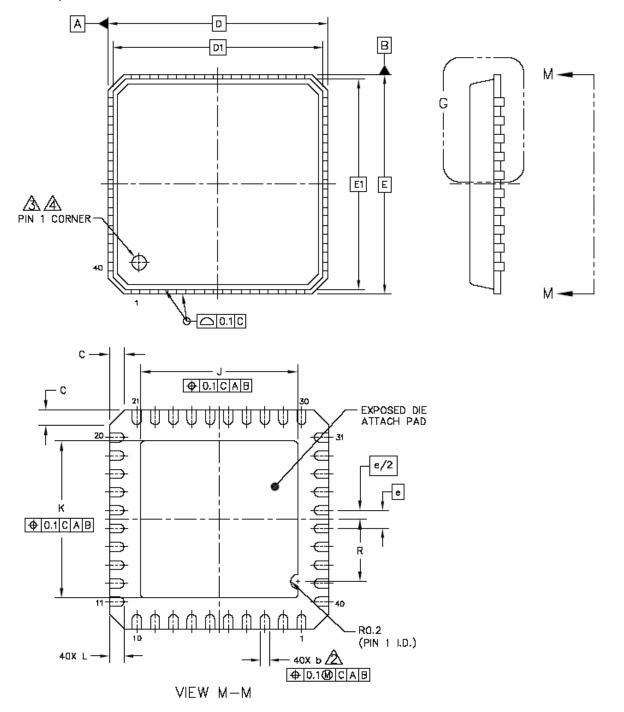

|        | kage Information                                               |    |

|        | .1. Package Drawing                                            |    |

| 5      | .2. Package Soldering                                          |    |

|        | 5.2.1. Background                                              |    |

|        | 5.2.2. Reference Reflow Temperature Curve                      | 79 |

| Appendix A. RSSI mapping table           | 81 |

|------------------------------------------|----|

| Appendix B. TX Power Configuration       | 82 |

| Appendix C. Register Descriptions        | 83 |

| C.1 Short Registers (SREG0x00~SREG0x3F)  | 83 |

| C.2 Long Registers (LREG0x200~LREG0x27F) | 98 |

#### **Abbreviations**

ADC Analog to Digital Converter

AES Advanced Encryption Standard

AGC Automation Gain Control

BER Bit Error Rate

CBC-MAC Cipher Block Chaining Message Authentication Code

CCA Clear Channel Assessment

CCM Counter Channel Mode

CSMA-CA Carrier Sense Multiple Access with Collision Avoidance

CTR Counter mode + CBC CW Continuous Wave

DSSS Direct Sequence Spread Spectrum

ESD Electronic Static Discharge EVM Error Vector Magnitude

FCC Federal Communication Commission

FIFO First In First Out

IEEE Institute of Electrical and Electronics Engineers

ISM Industrial Scientific and Medical

ITU-T International Telecommunication Union - Telecommunication

I/O Input / Output

I/Q In – phase / Quadrature – phase

Kbps Kilo bit per second LNA Low Noise Amplifier LO Local Oscillator

LQI Link Quality Indication

LSB Least Significant Bit / Byte

MSB Most Significant Bit / Byte

MAC Medium Access Control

MPDU MAC Protocol Data Unit

MSDU MAC Service Data Unit

NA Not Available NC Not Connected

O-QPSK Offset Quadrature Phase Shift Keying

PA Power Amplifier

PCB Printed Circuit Board

PHY Physical Layer

PLL Phase Locked Loop

PSDU PHY Service Data Unit

QFN Quad Flat No-lead Package

RF Radio Frequency

RSSI Receive Signal Strength Indicator

RX Receive

SPI Serial Peripheral Interface

TBD To Be Defined

T/R Transmit / Receive

TX Transmit

VCO Voltage Control Oscillator

## 1. Pin Configuration

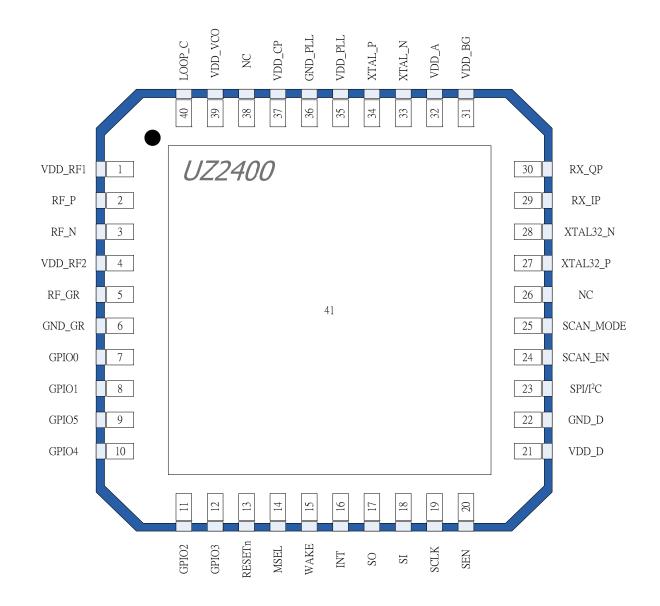

## 1.1. Device Pin Assignments

Figure 2. Pin assignments (top view)

## 1.2. Device Pin Descriptions

Pin type abbreviation: A = Analog, D = Digital, I = Input, O = Output

| Pin | Symbol    | Туре   | Description                                                           |

|-----|-----------|--------|-----------------------------------------------------------------------|

| 1   | VDD_RF1   | Power  | RF power supply. Bypass with a capacitor as close to the pin as       |

|     |           |        | possible.                                                             |

| 2   | RF_P*     | AIO    | Differential RF input/output (+)                                      |

| 3   | RF_N*     | AIO    | Differential RF input/output (-)                                      |

| 4   | VDD_RF2   | Power  | RF power supply. Bypass with a capacitor as close to the pin as       |

|     |           |        | possible.                                                             |

| 5   | VDD_GR*   | Power  | Guard ring power supply. Bypass with a capacitor as close to          |

|     |           |        | the pin as possible.                                                  |

| 6   | GND_GR    | Ground | Guard ring ground                                                     |

| 7   | GPIO0     | DIO    | General purpose digital I/O, also used as an external PA enable       |

| 8   | GPIO1     | DIO    | General purpose digital I/O, also used as an external TX/RX           |

|     |           |        | switch control                                                        |

| 9   | GPIO5     | DIO    | General purpose digital I/O                                           |

| 10  | GPIO4     | DIO    | General purpose digital I/O                                           |

| 11  | GPIO2     | DIO    | General purpose digital I/O, also used as an external TX/RX           |

|     |           |        | switch control                                                        |

| 12  | GPIO3     | DIO    | General purpose digital I/O                                           |

| 13  | RESETn    | DI     | Global hardware reset pin, active low                                 |

| 14  | MSEL      | DI     | SPI/memory interface selection                                        |

| 15  | WAKE      | DI     | External wake up trigger                                              |

| 16  | INT       | DO     | Interrupt pin to micro-processor                                      |

| 17  | SO        | DIO    | Serial interface data output from UZ2400 or I <sup>2</sup> C clock    |

| 18  | SI        | DIO    | Serial interface data input to UZ2400 or I <sup>2</sup> C data in/out |

| 19  | SCLK      | DI     | Serial interface clock                                                |

| 20  | SEN       | DI     | Serial interface enable                                               |

| 21  | VDD_D     | Power  | Digital circuit power supply                                          |

| 22  | GND_D     | Ground | Ground for digital circuit                                            |

| 23  | SPI/I2C   | DI     | SPI or I <sup>2</sup> C interface selection                           |

| 24  | SCAN_EN   | DI     | Scan insertion testing enable signal                                  |

| 25  | SCAN_MODE | DI     | Digital scan/test mode enable signal for chip testing purpose         |

| 26  | NC        |        | No connection (Do not connect power ground and signal)                |

| 27  | XTAL32_P* | ΑI     | 32 kHz Crystal input (+)                                              |

| 28  | XTAL32_N* | AI     | 32 kHz Crystal input (-)                                              |

| 29  | RX_IP     | AO     | Analog RX I channel output (+)                                        |

| 30  | RX_QP     | AO     | Analog RX Q channel output (+)                                        |

| 31  | VDD_BG    | Power  | Power supply for bandgap reference circuit. Bypass with a             |

|     |           |        | capacitor as close to the pin as possible.                            |

| 32 | VDD_A         | Power  | Power supply for analog circuit. Bypass with a capacitor as close |  |

|----|---------------|--------|-------------------------------------------------------------------|--|

|    |               |        | to the pin as possible.                                           |  |

| 33 | XTAL_N        | AI     | 20 MHz Crystal input (-)                                          |  |

| 34 | XTAL_P        | AI     | 20 MHz Crystal input (+)                                          |  |

| 35 | VDD_PLL       | Power  | PLL power supply. Bypass with a capacitor as close to the pin as  |  |

|    |               |        | possible.                                                         |  |

| 36 | GND_PLL       | Ground | Ground for PLL                                                    |  |

| 37 | VDD_CP        | Power  | Charge pump power supply. Bypass with a capacitor as close to     |  |

|    |               |        | the pin as possible.                                              |  |

| 38 | NC            |        | No connection                                                     |  |

| 39 | VDD_VCO       | Power  | VCO supply. Bypass with a capacitor as close to the pin as        |  |

|    |               |        | possible.                                                         |  |

| 40 | LOOP_C        |        | PLL loop filter external capacitor. Connected to external 100pF   |  |

|    |               |        | capacitor.                                                        |  |

| 41 | IC ground pad | Ground |                                                                   |  |

Table 1 Pin descriptions

\* *Caution*: ESD sensitive. Please refer to Section 2.5 for more information.

## 2. Electrical Characteristics

## 2.1. Absolute Maximum Ratings

| Parameters                            |      | Max     | Unit |

|---------------------------------------|------|---------|------|

| Storage temperature                   | -40  | +120    | °C   |

| Supply voltage VDD pin to ground      | -0.5 | +3.6    | V    |

| Voltage applied to inputs             | -0.5 | VDD+0.5 | V    |

| Short circuit duration, to GND or VDD |      | 5       | sec  |

Table 2 Absolute maximum ratings

## 2.2. Recommended Operating Conditions

Test conditions: VDD = 3 V

| Parameters                                   | Min       | Тур | Max       | Units |

|----------------------------------------------|-----------|-----|-----------|-------|

| *Ambient Operating Temperature               | -40       |     | +85       | °C    |

| Supply Voltage for RF, analog and digital    | 2.4       | 3   | 3.6       | V     |

| circuits                                     |           |     |           |       |

| Logical high input voltage (for DI type      | 0.5Xvdd_D |     |           | V     |

| pins)                                        |           |     |           |       |

| Logical low input voltage (for DI type pins) |           |     | 0.2Xvdd_D | V     |

Table 3 Recommended operating conditions

#### 2.3. DC Electrical Characteristics

Test conditions:  $T_A = 25^{\circ}C$ , VDD = 3 V

| Chip Mode  | Condition                   | Min | Тур | Max | Unit |

|------------|-----------------------------|-----|-----|-----|------|

| IDLE       | RF in reset mode.           |     | 7.6 |     | mA   |

|            | Regulator, oscillator and   |     |     |     |      |

|            | digital circuits are on.    |     |     |     |      |

| STANDBY    | All circuit power off, only |     | 3.5 |     | uA   |

|            | 100kHz oscillator is still  |     |     |     |      |

|            | on.                         |     |     |     |      |

| DEEP SLEEP | All circuit power off.      |     | 2   |     | uA   |

| ACTIVE: TX | At 0 dBm output power       |     | 23  |     | mA   |

| ACTIVE: RX |                             |     | 19  |     | mA   |

## 2.4. Radio Frequency AC Characteristics

#### 2.4.1. Receiver Radio Frequency AC Characteristics

Test conditions:  $T_A = 25$ °C, VDD = 3 V, LO frequency=2.445 GHz

| Parameters                 | Condition                                 | Min   | Тур | Max   | Unit |

|----------------------------|-------------------------------------------|-------|-----|-------|------|

| RF input frequency         | Compatible to IEEE802.15.4-2003           | 2.405 |     | 2.480 | GHz  |

| RF sensitivity             | At antenna input with O-QPSK signal       |       | -95 |       | dBm  |

| Maximum RF input           |                                           | +5    |     |       | dBm  |

| LO leakage                 | Measured at the balun matching network    |       | -60 |       | dBm  |

|                            | with the input frequency at 2.4 ~ 2.5 GHz |       |     |       |      |

| Noise figure               |                                           |       | 8   |       | dB   |

| (Including matching)       |                                           |       |     |       |      |

| Adjacent channel rejection | @+/-5 MHz                                 | 30    |     |       | dB   |

| Alternative channel        | @+/-10 MHz                                | 40    |     |       | dB   |

| rejection                  |                                           |       |     |       |      |

| RSSI range                 |                                           |       | 50  |       | dB   |

| RSSI error                 |                                           | -5    |     | 5     | dB   |

| Total RX current           |                                           |       | 19  |       | mA   |

#### 2.4.2. Transmitter Radio Frequency Characteristics

Test conditions:  $T_A = 25$ °C, VDD = 3 V, LO frequency=2.445 GHz

| Parameters                 | Condition                            | Min   | Тур  | Max   | Unit |

|----------------------------|--------------------------------------|-------|------|-------|------|

| RF carrier frequency       |                                      | 2.405 |      | 2.480 | GHz  |

| Maximum RF output          |                                      |       | 0    | 3     | dBm  |

| power                      |                                      |       |      |       |      |

| RF output power control    |                                      |       | 36   |       | dB   |

| range                      |                                      |       |      |       |      |

| TX gain control resolution |                                      | 0.5   | 1.25 | 1.4   | dB   |

| Carrier suppression        |                                      |       | -30  |       | dBc  |

| TX spectrum mask for       | Offset frequency > 3.5 MHz, at 0 dBm | -33   |      |       | dBm  |

| O-QPSK signal              | output power                         |       |      |       |      |

| TX EVM                     |                                      |       | 10%  |       |      |

| Total TX current           | At 0 dBm output power                |       | 23   |       | mA   |

#### 2.5. ESD Notice

For ESD HBM (Human Body Mode), all pins pass 1.5KV voltage requirement.

For ESD MM (Machine Mode), there are 5 pins that are sensitive to ESD; which are pin 2(RF\_P), pin 3(RF\_N),

pin 5(VDD\_GR), pin 27(XTAL32\_P) and pin 28(XTAL32\_N). PC board designer should take into account of the ESD sensitivity at these 5 pins.

#### 2.6. Peripheral Characteristics

UZ2400 has both slave mode SPI and  $I^2C$  interfaces. They can be used by the host MCU to access UZ2400 registers and FIFOs. The 4-wire SPI (SEN, SCLK, SI, SO) provides a high speed interface up to 8MHz on SCLK. Also, the 2-wire  $I^2C$  (SDA, SCL) interface provides another lower pin-count solution. The  $I^2C$  SDA and SCL share the same pins with SPI SI and SO respectively.

UZ2400 has six GPIO pins. Each can be configured either as an input or output pin. Users can use them for control or monitoring purposes. By simply configure GPIODIR register for input/output selection and GPIO for input/output data, users can gain full control over all six GPIOs.

When using SPI enhanced mode, GPIO4 and GPIO5 become part of SPI bus lines. GPIO0~GPIO3 remain unchanged. Please refer to Section 3.7.1 for detailed description.

#### 2.7. Power-on and Reset Characteristics

UZ2400 has built-in power-on reset (POR) circuit which automatically resets all digital registers when power is turned on. The 20MHz oscillator circuit starts to lock to the right clock frequency after power-on. The whole process takes 2ms for clock circuit to become stable and complete the power-on reset. It is highly recommended that the user waits at least 2ms before starting to access UZ2400.

For external hardware reset (warm start), external reset pin RESETn is internally pulled-high. UZ2400 will hold in reset state around 250usec after RESETn is released from low state.

## 2.8. Crystal Parameter Specifications

The clock system of UZ2400 can be separated to two parts, one is called main clock and the other is called sleep clock. Main clock is generated by 20MHz oscillator while sleep clock can be selected between 32.768KHz oscillator and 100KHz oscillator. Among all, the 20MHz and 32.768KHz clocks utilize an external crystal for generating the oscillation. The associated pins are XTAL\_P, XTAL\_N for 20MHz, and XTAL32\_P, XTAL32\_N for 32.768KHz crystal respectively. The frequency variation allowed for 20MHz crystal is from -60PPM to 60PPM. The 32.768KHz clock is the sleep clock for UZ2400. It provides real-time-clock based timing accuracy to count sleep duration.

## 3. Functional Description

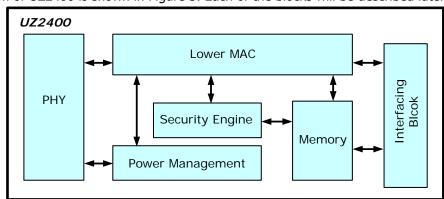

UZ2400 is composed of six blocks which are listed as followings,

- PHY block

- Lower MAC block

- Memory block

- Power management block

- Security block

- Interfacing block

The block diagram of UZ2400 is shown in Figure 3. Each of the blocks will be described later in this Chapter.

Figure 3 UZ2400 chip block diagram

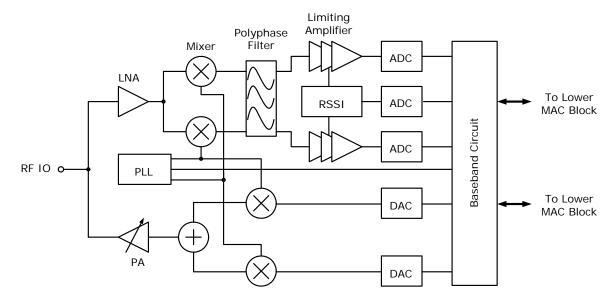

#### 3.1. PHY Block

The PHY (physical) block is compliant to IEEE 802.15.4-2003 2.4GHz band standard. The architecture is shown in Figure 4.

Figure 4 PHY block architecture

#### 3.1.1. IEEE 802.15.4-2003 PHY Introduction

UZ2400 provides a transceiver which is fully compatible to IEEE 802.15.4-2003 2.4GHz band PHY layer specifications. The key features of the PHY layer are described as below.

- Operating frequency range is from 2400 to 2483.5MHz, which includes 16 channels.

- It uses Offset QPSK (OQPSK) modulation to transmit data at 250kbps.

- Direct Sequence Spreading Spectrum (DSSS) is used in baseband algorithm to increase the SNR.

- It provides clear channel assessment (CCA) for CSMA-CA function.

- RSSI signal strength indicator is also provides.

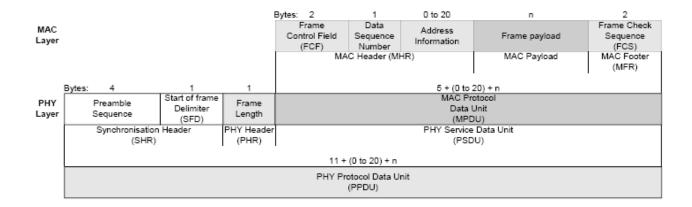

IEEE 802.15.4-2003 compliant packet includes 6 bytes of PHY header and 5~127 bytes of PHY payload. The 6 bytes of PHY header includes 4 bytes of preamble, 1 byte of start-of-frame delimiter (SFD), and 1 byte of payload length. Preamble and SFD are used for receiver packet detection and synchronization. The payload length is valid from 5 to 127 for an IEEE 802.15.4-2003 compliant packet.

The PHY payload includes variable bytes of MAC header, variable bytes of MAC payload and 2 bytes of cyclic redundant check (CRC, also called frame check sum, FCS). The packet format is as below:

| Pł       | HY header |        |                | PHY payload    |         |

|----------|-----------|--------|----------------|----------------|---------|

| Preamble | SFD       | Length | MAC header     | MAC payload    | CRC     |

| 4 bytes  | 1 byte    | 1 byte | Variable bytes | Variable bytes | 2 bytes |

Table 4 PHY layer frame format

For more information, please refer to IEEE 802.15.4-2003 standard.

#### 3.1.2. RSSI/ED and LQI

RSSI is used to report the signal strength of a received packet. UZ2400 attaches RSSI value following a received packet in RXFIFO every time a packet is received successfully. The format in RXFIFO is as below:

| LSB    |        |         |        |        | MSB    |

|--------|--------|---------|--------|--------|--------|

| 1 Byte | N Byte | N Bytes | 2 Byte | 1 Byte | 1 Byte |

| Frame  | Header | Payload | FCS    | LQI    | RSSI   |

| length |        |         |        |        |        |

Please refer to Appendix A for RSSI mapping table.

#### 3.1.3. CCA

Clear Channel Assessment (CCA) is designed to detect whether the current channel is occupied by other

devices and used in the CSMA-CA algorithm (see Section 3.2.5). UZ2400 provides three types of CCA functions: CS (Carrier Sense), ED (Energy Detection) and a combination of both.

- CS mode: The CCA/CS mode detects if there is an IEEE802.15.4 2.4G OQPSK signal occupying the current channel. To use this mode, set short register 0x3A bit7-6 to 0x01 and then configure the CS threshold by setting short register 0x3A bit5-2. The recommended threshold value is 0xE.

- ED mode: The CCA/ED mode detects if there is an in-band signal occupying the current channel. To use this mode, set short register 0x3A bit7-6 to 0x10 and then configure the ED threshold by setting short register 0x3F. For the threshold value mapping, please refer to Appendix A.

- Combination of CS and ED mode: This mode checks both the CS and ED results for CCA. To use this mode, set the short register 0x3A bit7-6 to 0x11 and set the CS and ED threshold as described above.

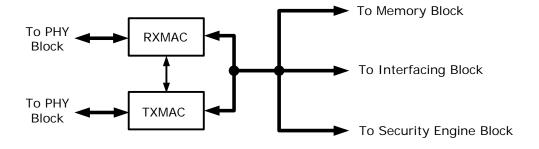

#### 3.2. Lower MAC Block

UZ2400 MAC provides plenty of hardware-assisted features to relieve the CPU/MCU power requirement. TX-MAC performs the CSMA-CA protocol to send a packet automatically. It also generates a 16-bit FCS automatically. In the Beacon-enabled mode, according to the Superframe architecture, TX-MAC will send the packet in normal FIFO during the CAP (contention access period), the packet in GTS1/2 FIFO during the CFP(contention free period) and the packet in beacon FIFO during the Superframe beacon period.

RX-MAC receives packets from the RX-Baseband. The received packet is put into RXFIFO and checked for FCS simultaneously. RX-MAC performs the packet filtering by destination address field and PAN-ID. If both match own identity and the FCS check is passed, an interrupt is issued to CPU/MCU. In the normal mode, unqualified packets are skipped. However, in promiscuous mode, any packet passing the FCS check is accepted and an interrupt will be issued. In the error mode, any packet is accepted with an interrupt issued. RX-MAC also informs TX-MAC to send an acknowledge packet automatically. This happens whenever a packet is successfully received and bit 5 of FCF is set to '1'. This will maintain the timing requirement of the acknowledge packet.

A 16-bit MAC timer is provided to facilitate the generation of the 15.36ms interrupt necessary for the ZigBee application.

Figure 5 Lower MAC block diagram

#### 3.2.1. IEEE 802.15.4-2003 MAC Introduction

IEEE802.15.4 MAC layer provides reliable wireless packet transactions between two nodes. It also handles data

and command transfer between the network and the physical layers. It handles the following tasks:

- Generating network beacons

- Synchronizing to beacons

- Supporting PAN association and disassociation

- Employing the CSMA-CA mechanism for channel access

- Handling and maintaining the guaranteed time slot mechanism

- Providing a reliable link between two peer MAC entities

The packet format of PHY and MAC layer is given below:

Figure 6 Packet format for PHY and MAC

The frame control field (FCF) format is two bytes as follow:

| Bits: 0-2     | 3                   | 4                | 5                   | 6            | 7-9      | 10-11                             | 12-13    | 14-15                        |

|---------------|---------------------|------------------|---------------------|--------------|----------|-----------------------------------|----------|------------------------------|

| Frame<br>Type | Security<br>Enabled | Frame<br>Pending | Acknowledge request | Intra<br>PAN | Reserved | Destination<br>addressing<br>mode | Reserved | Source<br>addressing<br>mode |

Figure 7 MAC frame control field

The frame check sequence (FCS) is CRC-16. The polynomial is degree 16:

$$G_{16}(x) = x^{16} + x^{12} + x^5 + 1$$

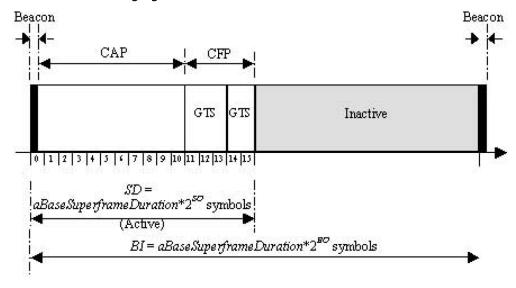

A PAN may be set up in one of the two basic configurations: Beacon-enabled and non-Beacon-enabled. In a non-Beacon-enabled network, devices may communicate with each other at any time after an initial association phase. Channel access and contention are managed using an unslotted CSMA-CA mechanism and any node-level synchronization must be performed at some higher layer. In a beacon-enabled network, the PAN coordinator periodically transmits a beacon which other devices use for both the synchronization and the

determination of the time when to enable transmission and reception of messages. This beacon message is used to define a Superframe structure that all nodes in the PAN should synchronize to. This Superframe structure is shown in the following figure.

Figure 8 The 802.15.4 MAC Superframe structure

The Superframe is divided into several sections whose lengths are configurable. There is an active period, during which the communication takes place, and an inactive period, during which the devices may turn off their transceivers in order to conserve the power. The active period is divided into 16 equally-spaced slots.

Immediately following the beacon is the contention access period (CAP). During this period, the devices may communicate using a slotted CSMACA mechanism. This is similar to the unslotted CSMA-CA, except that the back-off periods are aligned with the slot boundaries, meaning that the devices are contending for the right to transmit over the entire slots. The CAP must contain at least nine active period slots but may take up all 16.

Following the CAP is an optional contention free period (CFP), which may last up to seven active period slots. In the CFP, the devices are allocated GTS slots by the PAN coordinator. During a GTS, a device has the exclusive access to the channel and does not perform CSMA-CA. During one of these GTSs, a device may either transmit data to or receive data from its PAN coordinator, but not both. The length of a GTS must be an integral multiple of an active period slot. All GTSs must be contiguous in the CFP and are located at the end of the Superframe active period. A device may disable its transceiver during a GTS designated for another device in order to conserve power.

All devices must go through an initial association phase in order to become part of a PAN. This association is prompted by a higher layer service, but it uses primitives defined in the MAC to perform the associations. The MAC allows configurations to be set for starting a device as a PAN as a coordinator, allowing a coordinator to have devices associate with it, and performing the actual association of a device with some coordinator.

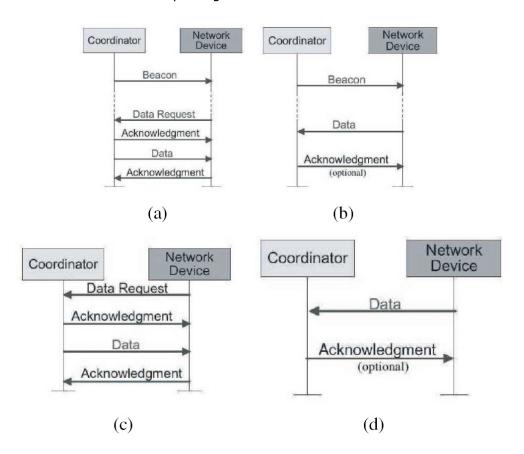

Once becoming part of a PAN, the data sent between a device and its coordinator is performed in one of the ways shown in the following figure. Note that acknowledgments are optional in all the transfers from a device to its coordinator, but they are required in transfers from the coordinator to a device. When transferring from a

coordinator to a device, the device must first request the data from the coordinator. In a non-Beacon-enabled network, devices must poll the coordinator for data at an application-specified rate, as there are no beacons to indicate to the device that there is data pending for it.

Figure 9 Data transfer between a coordinator and its devices a)Coordinator to Device with Beacons enabled, b) Device to Coordinator with Beacons enabled, c) Coordinator to Device with Beacons disabled, d)Device to Coordinator with Beacons disabled

#### 3.2.2. MAC Timer

UZ2400 has an internal MAC timer for ZigBee protocol use. It is a 16-bit down-counting timer ticking with half-symbol time (8us for IEEE802.15.4 standard). The beacon interval for ZigBee protocol is multiple times selectable of 15.36ms, which is 1920 times of 8us. Using MAC timer can relieve the timer resource from the MCU. The MAC timer can be triggered by writing HSYMTMR1 register to start downward counting. The timer generates a timer interrupt (half-symbol interrupt) when the down-counting reaches zero. The related registers are as below:

#### SREG0x28 HSYMTMR0

| SREGOx28, HSYMTMRO |                                       |       |       |       |       |      |       |

|--------------------|---------------------------------------|-------|-------|-------|-------|------|-------|

| Bit 7              | Bit 6                                 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit1 | Bit 0 |

|                    | Half-symbol tick timer low byte [7:0] |       |       |       |       |      |       |

|                    | R/W-0x00                              |       |       |       |       |      |       |

Bit 7:0 **HSYMTMRO**: Low byte of 16-bit half-symbol timer.

#### SREG0x29 HSYMTMR1

|       | SREG0x29, HSYMTMR1                     |       |       |       |       |      |       |

|-------|----------------------------------------|-------|-------|-------|-------|------|-------|

| Bit 7 | Bit 6                                  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit1 | Bit 0 |

|       | Half-symbol tick timer low byte [15:8] |       |       |       |       |      |       |

|       | R/W-0x00                               |       |       |       |       |      |       |

Bit 7:0 **HSYMTMR1**: High byte of 16-bit half-symbol timer.

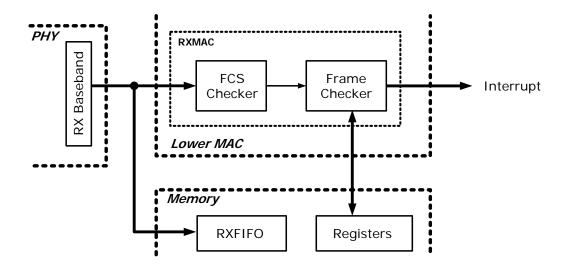

#### 3.2.3. RXMAC

RXMAC block will do the CRC checking, parsing the received frame type and do the address recognition before storing the received frame in the RXFIFO which is a 128-byte dual port register file. The received frame will be stored in RXFIFO one packet at a time. A byte of length will be appended in front of the MPDU, so that the host can decode the frame correctly. There are also 9 bytes of information attached: LQI, RSSI, Frame Timer (4 bytes), Superframe Counter (3 bytes)

The behavior of RXFIFO follows a certain rule: When a received packet is not filtered or dropped out, a received interrupt/status will be issued. The interrupt is a read-to-clear type to save the host operation time. However, the RXFIFO is flushed only by the following three ways: (1) the host reads the first byte of the packet, (2) the host issues an RX flush and (3) the software reset. Please note that once the first byte of RXFIFO is read, RXFIFO is ready to receive the next packet. So it is suggested that the programmer reads back all data without any interrupt or jumping to other process.

RXMAC recognized a valid packet according to rules provided in Section 7.5.6.2 of IEEE802.15.4-2003 specification. The acceptance rules are:

- (1) The frame type subfields shall not contain an illegal frame type.

- (2) If the frame type indicates that the frame is a beacon frame, the source PAN identifier shall match macPANId unless macPANId is equal to 0 x ffff, in which case the beacon frame shall be accepted regardless of the source PAN identifier.

- (3) If a destination PAN identifier is included in the frame, it shall match macPANId or shall be the broadcast PAN identifier (0xFFFF).

- (4) If a short destination address is included in the frame, it shall match either macShortAddress or the broadcast address (0xFFFF). Otherwise, if an extended destination address is included in the frame, it shall match aExtendedAddress.

- (5) If only source addressing fields are included in a data or MAC command frame, the frame shall be accepted only if the device is a PAN coordinator and the source PAN identifier matches macPANId.

If the above conditions are met, RXMAC will issue RX interrupt to host device to indicate a valid packet is received. UZ2400 RXMAC also supports promiscuous mode and error mode. Promiscuous mode is supported to receive all FCS-ok packets. Error mode is supported to receive all packets that successfully correlate with the PHY level preamble and delimiter. Under these two conditions, RXMAC issues RX interrupt, too.

UZ2400 RXMAC supports automatic ACK reply. If and only if the five conditions mentioned above are met, and AckReq bit in frame-control field of header of the received packet is set, an ACK packet will be sent by TXMAC automatically in the meantime. The sequence number will be the same as incoming packet.

When an encrypted packet is received, RXMAC will not inform the security module directly. Instead, it issues a security interrupt. Then the host can decide whether to decrypt or ignore it.

Figure 10 RXMAC block diagram

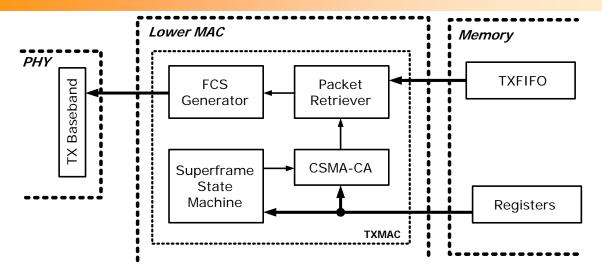

#### 3.2.4. TXMAC

The block diagram of TXMAC is shown in Figure 11 below. TXMAC performs three major tasks that conform to the IEEE 802.15.4 standard. They are:

- TXFIFO control

- Automatic CSMA-CA and timing alignments.

- Hardware Superframe handling.

For TXFIFO control function, TXMAC controls four FIFOs including the beacon, the normal and the two GTS FIFOs. When each of the FIFOs is triggered, TXMAC performs the CSMA-CA algorithm, sends the packet to TXBB at the right time, handles the retransmission if ACK is required but not received, and generates FCS bytes automatically. Automatic CSMA-CA algorithm performs the timing alignments such as LIFS, SIFS and ACK turnaround time. User can simply program the parameters of CSMA-CA algorithm and TXMAC will perform corresponding tasks automatically.

For hardware Superframe handling under Beacon-enabled operation, TXMAC builds up the timing frame of a Superframe automatically. This greatly alleviates the loading of upper MCU. TXMAC calculates the timing for CAP, CFP, INACTIVE and each time slot then perform corresponding task if there is any. TXMAC sends the beacon, the normal and the GTS FIFOs at the right time of each transmission automatically. This largely reduces the complexity of the Beacon-enabled mode of IEEE 802.15.4.

Figure 11 TXMAC block diagram

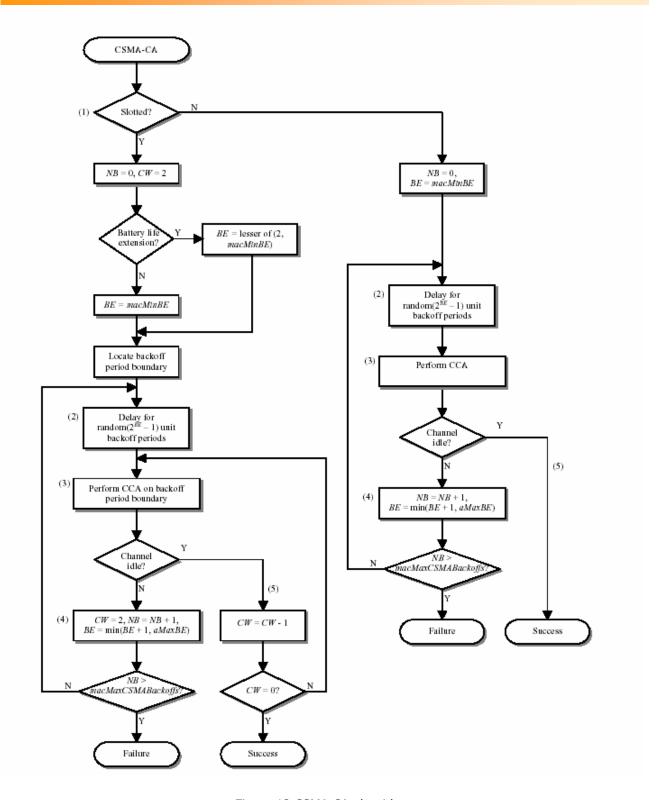

#### 3.2.5. CSMA-CA

The LR-WPAN uses two types of channel access mechanism, un-slotted CSMA-CA and slotted CSMA-CA. This depends on the network configuration. Non-beacon-enabled networks use an un-slotted CSMA-CA while Beacon-enabled networks use slotted CSMA-CA.

For un-slotted CSMA-CA, each time a device wishes to transmit data frames or MAC commands, it will wait for a random back-off. If the device finds that the channel is idle, it will wait for another extra random back-off before transmitting its data. This extra random back-off reduces the chance of on-air data collision. If a channel is busy, following a random back-off, the device will try to access the channel again. Once the device finds that the channel becomes idle, it will wait for another extra random back-off before transmitting its data. If the channel is always busy and the times of failure is more than macMaxCSMABack-offs (defined in IEEE 802.15.4, this parameter equals 4 by default), the process is considered failed. Acknowledgment frames will be sent without using a CSMA-CA mechanism.

You can modify the parameters of CAMA-CA of UZ2400 at Short register 0x11 as follow.

- SREG0x11[7] defines whether CSMA-CA algorithm is used or not. Set SREG0x11[7] to '1' disables CSMA-CA, otherwise else.

- SREG0x11[4-3] defines the maximum value of the back-off exponent in the CSMA-CA algorithm. Note that if this value is set to 0, collision avoidance is disabled during the first iteration of the algorithm. Also note that for the slotted version of the CSMACA algorithm with the battery life extension enabled, the minimum value of the back-off exponent will be the lesser of 2 and the value of macMinBE.

- SREG0x11[2:0] defines the maximum number of back-offs which the CSMA-CA algorithm will attempt before declaring a channel access failure. The range is between 0 and 5.

Figure 12 CSMA-CA algorithm

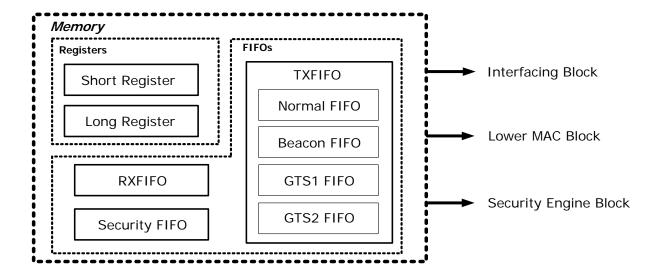

#### 3.3. Memory Block

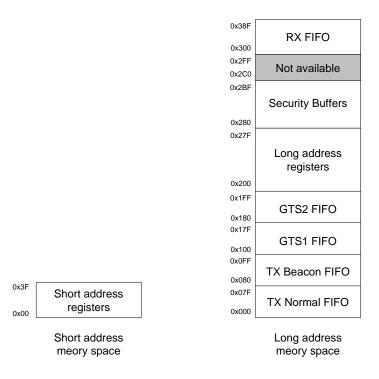

The memory block (including registers and FIFOs) of UZ2400 is implemented by SRAM. It is composed of registers and FIFOs as shown below:

#### Registers

- Short register (6-bit short addressing mode register, total 64 bytes)

- Long register (10-bit long addressing mode register, total 128 bytes)

#### **FIFOs**

- TX FIFO Normal (128 bytes)

- TX FIFO Beacon (128 bytes)

- TX FIFO GTS1 (128 bytes)

- TX FIFO GTS2 (128 bytes)

- Security Key FIFO (64 bytes)

- RX FIFO (128 + 16 bytes)

Figure 13 Memory block diagram

FIFO Mapping

| Short Address    |

|------------------|

| Control Register |

| (64 bytes)       |

| bit [7]            | bit [6:1]        | bit [0]           |

|--------------------|------------------|-------------------|

| Short Address<br>0 | $0x3F \sim 0x00$ | Read/Write<br>0 1 |

TXFIFO (512 bytes)

| bit [11]       | bit [10:1]         | bit [0]           |

|----------------|--------------------|-------------------|

| Long Address 1 | $0x1FF \sim 0x000$ | Read/Write<br>0 1 |

Long Address Control Register (128 bytes)

| bit [11]     | bit [10:1]         | bit [0]           |

|--------------|--------------------|-------------------|

| Long Address | $0x27F \sim 0x200$ | Read/Write<br>0 1 |

Security (64 bytes)

| bit [11]       | bit [10:1]         | bit [0]        |

|----------------|--------------------|----------------|

| Long Address 1 | $0x2BE \sim 0x280$ | Read/Write 0 1 |

RXFIFO (128 + 16 bytes)

| 1   | bit [11]        | bit [10:1]                    | bit [0]           |

|-----|-----------------|-------------------------------|-------------------|

| Loi | ng Address<br>1 | $0x38F \sim 0x37F \sim 0x300$ | Read/Write<br>0 1 |

Registers provide control bits and status flags for UZ2400 operations, including transmission, reception, interrupt control, timer, MAC/baseband/RF parameter settings, security, etc. Short registers are accessed by short addressing mode with valid addresses ranging from 0x00 to 0x3F. Long registers are accessed by long addressing mode with valid addresses ranging from 0x200 to 0x27F. The length of the address differs between the two modes. Please refer to Section 3.7.1 and 3.7.2 for detailed addressing rules for SPI and  $I^2C$  interface.

FIFOs serve as the temporary data buffers for data transmission, reception and security keys. Each FIFO holds one packet only at a time. The transmission FIFO is called TXFIFO. TXFIFO is composed of four 128-byte FIFOs for different purposes, namely Normal FIFO, Beacon FIFO, GTS1 FIFO and GTS2 FIFO. The receiving FIFO is called RXFIFO. RXFIFO is composed of one 144-byte FIFO. The final part is called Security Key FIFO. Security Key FIFO is composed of one 64-bite FIFO and is capable of holding four 16-byte security keys for secured operation. The beacon and GTS2 FIFOs share the same security key space. Please refer to Section 4.2 for

further information about registers and FIFOs.

#### 3.3.1. Registers

#### Short Registers

Short registers are accessed by short addressing mode with valid addresses ranging from 0x00 to 0x3F. Together with long registers, they provide control bits and status flags for UZ2400 operations, including transmission, reception, interrupt control, timer, MAC/baseband/RF parameter settings, security, etc. Short registers are accessed faster than long registers.

#### Long Registers

Long registers are accessed by long addressing mode with valid addresses ranging from 0x200 to 0x27F. Together with short registers, they provide control bits and status flags for UZ2400 operations, including transmission, reception, interrupt control, timer, MAC/baseband/RF parameter settings, security, etc. Long registers are accessed slower than short registers.

#### 3.3.2. FIFOs

#### **TXFIFO**

TXMAC gets data to transmit from four TXFIFOs: beacon, normal, GTS1 and GTS2. According to different conditions, different FIFO is selected. All four TXFIFOs are 128 bytes in length, which can contain one 802.15.4 MAC packet at a time.

In non-beacon-enabled mode, TXMAC always gets data from normal FIFO. In beacon-enabled mode, TXMAC gets data from beacon FIFO during beacon slot. It gets data from normal FIFO during CAP slots and GTS1/2 FIFOs during CFP slots. All of the four FIFOs can be accessed by SPI/I2C interface.

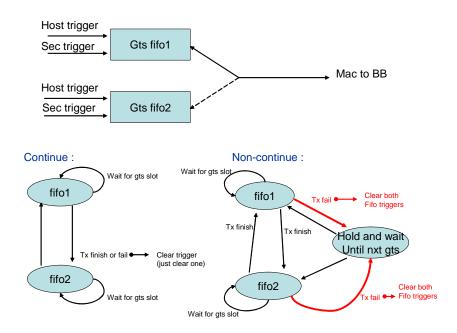

GTS1 and GTS2 FIFOs are ping-pong FIFOs. They are designed for QoS(quality of service) during beaconenabled mode. The two FIFOs can be assigned to different GTS slots. If they are in the same slot, they take turns within that GTS slot if both are triggered. GTS1/2 FIFO can be triggered before their GTS slot comes. Below is GTS FIFO's behavior:

Figure 14 GTS FIFO selection

#### **RXFIFO**

RXFIFO is a 144-byte FIFO memory to store the incoming packet. It's designed to store one packet at a time. Section 3.2.3 details the RXMAC behavior.

#### Security FIFO

Security FIFO holds corresponding key of each FIFO. The address mapping is as below:

| Address     | Description             |

|-------------|-------------------------|

| 280h ~ 28Fh | TX Normal FIFO key      |

| 290h ~ 29Fh | TX GTS1 FIFO key        |

| 2A0h ~ 2AFh | TX GTS2/Beacon FIFO key |

| 2B0h ~ 2BFh | RX FIFO key             |

## 3.4. Power Management Block

Almost all wireless sensor network applications require low-power consumptions to lengthen the battery life. Typical power consumption of a battery-powered device is such that the deployed device could operate over years without replacing its battery. The UZ2400 achieves low active current consumption of both the digital and the RF/analog circuits by controlling the supply voltage and using low-power architecture. The sleep current for UZ2400 can be as low as 2uA only. During the sleep mode, the data in the digital registers/FIFOs are retained. UZ2400 has four power saving modes that will be further described in Section 3.4.5.

#### 3.4.1. Power Supply Scheme

The table below lists the recommended external bypass capacitors for each pin of the UZ2400. For the two power supply pins (pin No.1 and 31), they need an extra bypass capacitor in parallel for decoupling purpose while the rest of the power supply pins require only one bypass capacitor. The path length between the bypass capacitors to each pin should be made as short as possible.

| Pin | Symbol  | Bypass Capacitor 1 | Bypass Capacitor 2 |  |

|-----|---------|--------------------|--------------------|--|

| 1   | VDD_RF1 | 47 pF              | 10 nF              |  |

| 4   | VDD_RF2 | 47 pF              |                    |  |

| 5   | VDD_GR  | 100 nF             |                    |  |

| 21  | VDD_D   | 10 nF              |                    |  |

| 31  | VDD_BG  | 47 pF              | 10 nF              |  |

| 32  | VDD_A   | 47 pF              |                    |  |

| 35  | VDD_PLL | 47 pF              |                    |  |

| 37  | VDD_CP  | 10 nF              |                    |  |

| 39  | VDD_VCO | 1 uF               |                    |  |

Table 5 Recommended external bypass capacitors

#### 3.4.2. Voltage Regulator

There is an individual voltage regulator for each supply voltage pin of the UZ2400. No external stabilizing capacitor is needed for each of the voltage regulators. All the regulators supply a 1.8V output to internal circuit nets.

#### 3.4.3. Battery Monitor

UZ2400 provides a function to monitor the system supplied voltage. A 4-bit voltage threshold can be configured so that when the supplied voltage is lower than the threshold, the system will be notified. For battery monitor function, please refer to Section 4.7.

#### 3.4.4. Power-on Reset

UZ2400 has a built-in power-on reset (POR) circuit which automatically resets all digital registers whenever the power is turned on. The 20MHz oscillator circuit starts to lock to the right clock frequency after power-on. The whole process takes 2ms for clock circuit to become stable and complete the power-on reset. It is highly recommended that the user waits at least 2ms before starting to access UZ2400.

#### 3.4.5. Power Modes

The power modes of UZ2400 are classified into the following four modes:

■ ACTIVE : Fully turned on with two sub-modes designated as TX-ACTIVE and RX-ACTIVE

■ IDLE : RF shutdown mode

■ STANDBY : RF/MAC/BB shutdown with sleep clock remains active

■ DEEP\_SLEEP : All power is shutdown except the power to the digital circuits, register and FIFO data

are retained.

The sleep mode mentioned later means both the STANDBY mode and the DEEP\_SLEEP mode. The only difference between the STANDBY mode and the DEEP SLEEP mode is the power status of the Sleep clock. The IDLE mode is rarely used because the device should at least always turns on its RX circuit to capture the on-air RF signals.

The power management control is used for the low power operation of the MAC and the baseband modules. It manages to turn on and off the 20MHz clock when the ASIC goes into the sleep mode. By turning off 20MHz clock, the MAC and baseband circuits become inactive regardless whether their power supplies exist or not.

All the digital modules are clock-gated automatically. That means only when a module is functioning, its clock would then be turned on. For example, the clock of the security module is turned off if the security feature is disabled. This approach efficiently decreases a certain amount of current consumption.

With the help of on-chip main and remain counters, UZ2400 is able to switch between ACTIVE and STANDBY modes for both beacon and non-beacon modes. Detailed descriptions are available in Section 3.4.6. If the DEEP\_SLEEP mode is desired instead of the STANDBY mode, the host MCU has to control the timing of sleeping process and the Beacon-enabled mode is not suggested under this operation.

#### 3.4.6. Counters for Power Saving Modes

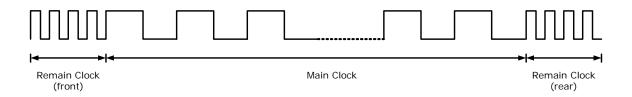

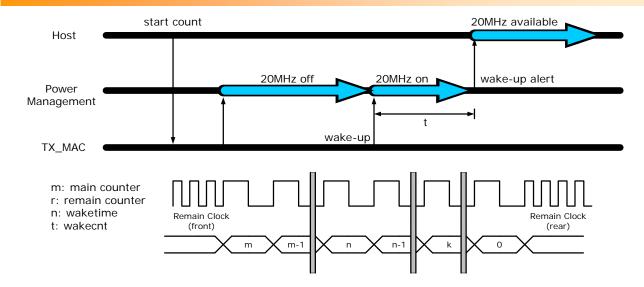

There are two dedicated time counters in UZ2400 for sleep mode operation. One is called main counter and the other is called remain counter. The unit of tick differs between the two counters since the clock for main counter is driven by Sleep clock which is either 100kHz (on-chip internal clock) or 32.768kHz (off-chip external clock). The remain counter is driven by 20MHz clock. The sleeping reference interval is calculated using the combination of the two time counts of main counter and remain counter to achieve timing accuracy.

#### Sleeping Reference Interval

The sleeping reference interval is composed of three parts. In the beginning, there is the front remain clock period. In the middle, there is the main clock period which is the major component of sleeping reference interval. In the end, there is the rear remain clock period which is identical to the front clock period. The front and rear remain clock periods increase the accuracy of sleeping intervals.

Figure 15 Composition of sleeping reference interval

#### Sleep Alert (SLPIF, SREGOx31[7])

The sleep alert is issued by TXMAC on the boundary between the active (composed of CAP and CFP) and the inactive period which is defined in the Beacon-enabled mode in IEEE 802.15.4 standard. Sleep alert is an interrupt event which informs the host MCU that the inactive period has been started under Beacon-enabled mode. For Non-beacon-enabled mode, sleep alert is disabled.

#### Sleep Acknowledgement (SLPACK, SREG0x35[7])

For Beacon-enabled mode, the SLPACK (SREG0x35[7]) should be issued by host MCU to initiate the sleep process. The sleep acknowledgement also turns off the PHY block.

#### Start Count (StartCnt, LREG0x229[7])

For Non-beacon-enabled mode, the StartCnt (LREG0x229[7]) should be set to "1" to initiate the sleep process. The StartCnt also turns off the PHY block and starts the sleep reference clock under Non-beacon-enabled mode.

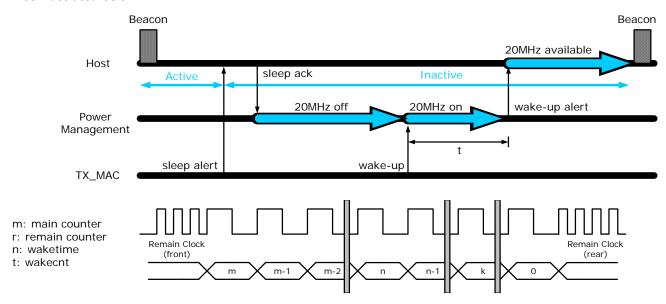

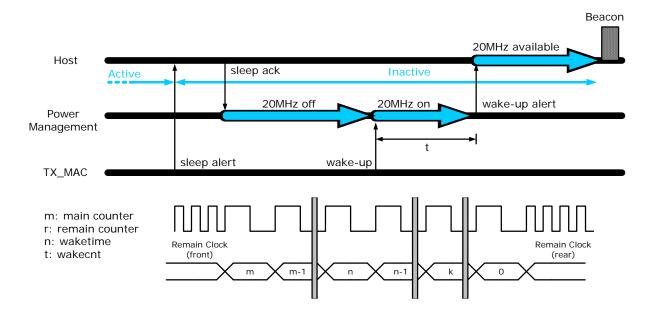

#### Wake-up and Wake-up Alert (WAKEIF, SREG0x31[6])

UZ2400 wakes up when the wake-time (waketime, LREG0x222, LREG0x223) is reached. The 20MHz oscillator is restarted after the wake-up signal asserts itself. Since the 20MHz oscillator needs 2~3 ms to become stable, the 20MHz clock is not enabled immediately once the 20MHz oscillator is restarted. The 20MHz clock will be enabled only when one extra wake-count (WAKECNT, SREG0x35, SREG0x36) is reached.

#### IEEE 802.15.4 Application Scenarios

The followings are three power saving examples demonstrating the switching between the ACTIVE and the STANDBY modes for typical 802.15.4 application scenarios:

- Beacon-enabled coordinator

- Beacon-enabled device

- Non-beacon-enabled coordinator or device

For Beacon-enabled coordinator, the sum of the main counter and the front and rear remain counters is the beacon interval. Coordinator sends beacon packets according to the interval. A sleep alert is issued by TX\_MAC to host MCU at the end of the active period. Host MCU issues a sleep acknowledgement to initiate the sleep process. The coordinator has to prepare the beacon packet in advance. So a "waketime" is designed into the UZ2400 in order to wake it up earlier to allow power on the 20MHz oscillator and make it stable. When the waittime matches the main counter (down counter), the 20MHz clock is enabled. Because it takes certain time for the 20MHz clock to become stable, the clock is not provided until the "waitcnt" is exceeded. Therefore the waittime should be longer than the waitcnt. After the rear remain counter reaches its end, another beacon is transmitted and this gives rise to next Superframe.

For Beacon-enabled device, the sum of the main counter and the front and rear remain counters is the inactive period. A sleep alert is issued by TX\_MAC to host MCU at the end of active period. Host MCU issues sleep acknowledgement to initiate the sleep process. The device has to be ready for receiving the beacon packet in advance. So a "waketime" is designed in UZ2400 in order to wake up earlier to allow power on the 20MHz oscillator and make it stable. When the waittime matches the main counter (down counter), the 20MHz clock is

enabled. Because it takes certain time for the 20MHz clock to become stable, the clock is not provided until the "waitcnt" is exceeded. Therefore the waittime should be longer than the waitcnt. Asthe rear remain counter reaches its end, a beacon should be received and this indicates a next Superframe.

In the Non-beacon-enabled mode, the same idea is adopted. The only difference is that the host MCU has to set the StartCnt bit to initiate the sleep process. The sleep reference clock is started right after the StartCnt bit is set. The wake-up process is identical to the beacon mode operation. The actual sleep time is r(front) + m - n as illustrated below.

Figure 16 Sleeping timing diagram for Beacon-enabled coordinator

Figure 17 Sleeping timing diagram for Beacon-enabled device

Figure 18 Sleeping timing diagram for Non-beacon-enabled coordinator or device

#### Main Counter (TXMAINCNT, LREGOx226, LREGOx227, LREGOx228, LREGOx229)

The main counter uses Sleep clock to count. The Sleep clock can be selected by LREG0x207[7:6] between the external 32.76kHz clock or the internal 100kHz clock. An extra clock accuracy calibration should be performed when using the internal 100kHz as Sleep clock. Please refer to Section 4.5.1 for detailed calibration procedure. The count is stored from LREG0x226 to LREG0x229.

#### Remain Counter (TXREMCNT, LREGOx224, LREGOx225)

The remain counter uses 20MHz clock to count. The count is stored in LREG0x24 and LREG0x25.

#### Waketime (WAKETIME, LREGOx222, LREGOx223)

The waketime is denoted with the number "n" in the Figure 16, Figure 17 and Figure 18. It indicates the time when the 20MHz oscillator should wake up from the sleep status.

#### Wake count (WAKECNT, SREGOx35, SREGOx36)

The WAKECNT is the time count "t" in between the restart of the 20MHz oscillator and when it becomes stable and available. It ticks according to the chosen Sleep clock.

#### Enter STANDBY or DEEP\_SLEEP Modes

- STANDBY mode

- ◆ The UZ2400 STANDBY modes can be activated by setting the SLPACK (SREG0x35[7]) under Beacon-enabled mode or setting the StartCnt (LREG0x229[7]) under Non-beacon-enabled mode. When either of these two bits is set, UZ2400 turns off the voltage regulators and the RF circuits enter the sleep mode. During the sleep mode, both long and short registers are accessible and their contents are retained.

- DEEP\_SLEEP mode

- ◆ To enter DEEP\_SLEEP mode for sleep status, user has to disable the Sleep clock which is always turned-on in STANDBY mode to further reduce the current consumption. DEEP\_SLEEP mode is only available under Non-beacon-enabled mode. It is not allowed to turn off the Sleep clock to go into

sleep under Beacon-enabled mode because the Sleep clock has to count the boundaries of Superframe. In Non-beacon-enabled mode, set SLPACK (SREG0x35[7]) to "1" will enforce UZ2400 to sleep without turning on the Sleep clock to generate the sleep reference clock.

#### Wake-up

UZ2400 has two wake-up modes: timed wake-up and immediate wake-up.

- Timed wake-up

- ◆ Timed wake-up is described in the above under both the beacon and non-beacon modes. However, if user sets both main counter and remain counter to zero, UZ2400 will not wake up unless an immediate wake-up is triggered.

- Immediate wake-up

- ◆ UZ2400 can be awakened externally by WAKE (pin 15). SREG0x0D[5] enables the WAKE pin. SREG0x0D[6] controls the polarity of the WAKE pin. Be sure to set SREG0x22[7] to "1" to enable the Immediate wake-up mode before sleep.

- ◆ UZ2400 can also be awakened by setting SREG0x22[6] to "1" and back to "0", the immediate wake-up mode is then entered.

- ◆ Another fast way to wake up UZ2400 is to set SOFTRST. Setting SREG0x2A[2]="1" resets the power management circuits, including the sleep registers.

#### 3.4.7. Hardware Acknowledgement

Following the IEEE 802.15.4 standard, the request for remote acknowledgement of a transmitted packet can be enabled or disabled by setting its header field. The header format is shown as below:

| Octets: 2        | 1                  | 0/2                                                                                                | 0/2/8 | 0/2              | 0/2/8 | variable       | 2   |

|------------------|--------------------|----------------------------------------------------------------------------------------------------|-------|------------------|-------|----------------|-----|

| Frame<br>control | Sequence<br>number | Destination PAN identifier Destination address Source PAN identifier Source pAN identifier address |       | Frame<br>payload | FCS   |                |     |

|                  |                    | Addressing fields                                                                                  |       |                  |       |                |     |

| MHR              |                    |                                                                                                    |       |                  |       | MAC<br>payload | MFR |

Figure 34—General MAC frame format

| Bits: 0-2     | 3                   | 4                | 5               | 6             | 7–9      | 10-11                       | 12-13    | 14–15                        |

|---------------|---------------------|------------------|-----------------|---------------|----------|-----------------------------|----------|------------------------------|

| Frame<br>type | Security<br>enabled | Frame<br>pending | Ack.<br>request | Intra-<br>PAN | Reserved | Dest.<br>addressing<br>mode | Reserved | Source<br>addressing<br>mode |

Figure 35—Format of the frame control field

Bit 5 of the "Frame control" field indicates whether the frame needs an acknowledgement or not. Users should prepare the header information correctly and write it into TXFIFO. If "Ack request" bit-field is set to "1", the receiver of this packet is required to send the ACK packet back. If the ACK frame from the remote receiver is not received, the transmitter should send the packet again and again till the maximum retransmission times is reached.

UZ2400 has built-in circuit to facilitate the acknowledge protocol automatically. For transmitting side, UZ2400 supports auto-retransmission. For receiving side, UZ2400 supports auto-acknowledgement. Each of the two sides needs to set corresponding registers correctly to utilize the functions.

#### Auto-retransmission on TX Side

For TXMAC to retransmit a packet automatically when ACK is not received, "TXNACKREQ" (SREG0x1B[2] for TX normal FIFO) is required to be set to "1". Please refer to Section 4.3.1 for more detailed description

#### Auto-acknowledgement on RX Side

RXMAC of UZ2400 will automatically reply ACK packet by default if "Ack request" in the frame header is set to "1". This auto-acknowledgement feature can be disabled by setting NOACKRSP (SREG0x00[5]) to "1".

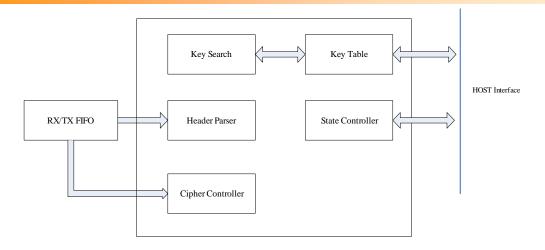

#### 3.5. Security Engine Block

The Security module provides the security engine for UZ2400 MAC, which is compatible to IEEE802.15.4-2003 (also adopted by Zigbee). In addition to MAC layer security requirements, UZ2400 also provides a way called "upper-layer security" for network or application layer use. For more detailed information, please refer to Section 4.8.

Following are the features of the UZ2400 Security Engine Block:

- Transmit encryption and receive decryption

- Seven modes of Security suites are provided:

- ◆ AES-CTR

- ♦ AES-CCM-128

- ♦ AES-CCM-64

- ♦ AES-CCM-32

- AES-CRC-MAC-128

- AES-CRC-MAC-64

- ◆ AES-CRC-MAC-32

- 64 x 8bits Security RAM for security suite. It stores one receive key and three transmit keys for TXFIFOs. Beacon FIFO and GTS2 FIFO share the same key space since they will not conflict with each other. Normal FIFO and GTS1 FIFO both have their own transmit keys.

- Security of APL and NWK layers can be achieved using the same engine. The upper-layer security function is compliant to ZigBee V1.0 specifications.

Figure 19 Security engine block diagram

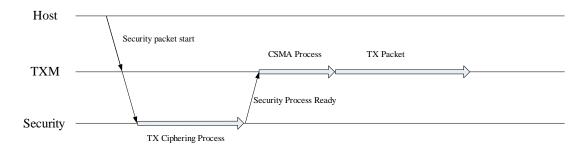

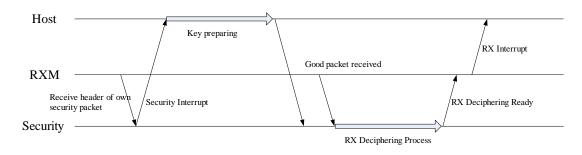

#### Transmit Flow

# Receive Flow

Figure 20 Security engine flow chart

# 3.6. Analog Circuits

# 3.6.1. Crystal Oscillators

The table below lists the parameters of the 20 MHz crystal oscillator used in UZ2400. This clock is exportable at pin 26. Optional frequencies are selectable among 20 MHz/10 MHz/5 MHz/2.5 MHz. The crystal can be shared with a host MCU.

By default, 20MHz crystal is suggested for most applications. User has to select 20MHz crystal which meets the following requirements in order to operate UZ2400 properly.

| Parameter                  | Min | Тур | Max | Unit |

|----------------------------|-----|-----|-----|------|

| Crystal Frequency          |     | 20  |     | MHz  |

| Crystal Frequency Accuracy | -40 |     | 40  | ppm  |

Table 6 Requirements for 20MHz crystal

| Parameter                | Condition | Min       | Тур | Max | Unit |

|--------------------------|-----------|-----------|-----|-----|------|

| ESR                      |           |           | 80  |     | Ohm  |

| CO                       |           |           | 5   |     | pF   |

| CL                       |           |           | 27  |     | pF   |

| Crystal tuning range     |           |           | 5   |     | pF   |

| Crystal tuning step size |           |           | 0.5 |     | pF   |

|                          | CRYSTAL   | TUNING US | ING |     |      |

| Start-up time            |           |           | 250 |     | us   |

| Crystal tuning step size | CL=27.5pF |           | 1.2 |     | PPM  |

| Crystal tuning range     | CL=22pF   |           | 21  |     | PPM  |

Table 7 On-chip Crystal Frequency Tuning (eCERO FL-200-0006-G)

| Parameter                | Condition | Min       | Тур  | Max | Unit |

|--------------------------|-----------|-----------|------|-----|------|

| ESR                      |           |           | 80   |     | Ohm  |

| C0                       |           |           | 1.04 |     | pF   |

| CL                       |           |           | 12   |     | pF   |

| Crystal tuning range     |           |           | 8    |     | pF   |

| Crystal tuning step size |           |           | 0.5  |     | pF   |

|                          | CRYSTAL   | TUNING US | ING  |     |      |

| Start-up time            |           |           | 250  |     | us   |

| Crystal tuning step size | CL=27.5pF |           | -0.6 |     | PPM  |

| Crystal tuning range     | CL=22pF   |           | -50  |     | PPM  |

Table 8 On-chip Crystal Frequency Tuning (NDK NX3225SA)

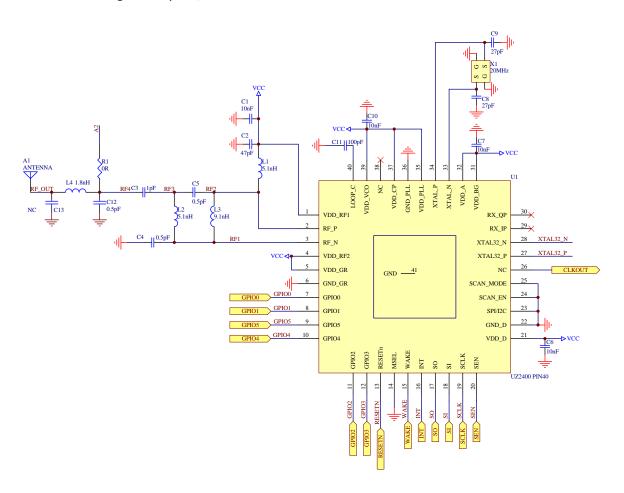

### 3.6.2. PLL Frequency Synthesizer

The loop filers of the Phase-Lock Loop (PLL) in the frequency synthesizer are integrated into UZ2400 except one external capacitor which should be connected between pin 40 and the ground. The board layout around pin 40 should be carefully designed to avoid EMI (electro magnetic interference) in order to keep the PLL stable. The recommended value of this external capacitor is 100 pF.

# 3.6.3. Internal 100kHz Sleep Clock Oscillator for Sleep Clock

There is a free-running 100 kHz sleep clock oscillator integrated into UZ2400. No external component is needed for the operation of this sleep clock. User has to calibrate this 100kHz Sleep clock before an application starts. Please refer to Section 4.5.1 Step 4. for calibration procedures.

# 3.6.4. 32.768 kHz Crystal Oscillator for Sleep Clock

The table below lists the parameters of the 32.768 kHz crystal oscillator used in UZ2400. The external 32.768kHz crystal greatly enhance the accuracy of this oscillator so that it does not need calibration any more.

| Parameter         | Min | Тур    | Max | Unit |

|-------------------|-----|--------|-----|------|

| Crystal Frequency |     | 32.768 |     | kHz  |

| Frequency Offset  | -20 |        | 20  | PPM  |

| Shunt Capacitance |     | 33     |     | pF   |

| Series Resistance |     | 10     |     | ΜΩ   |

| Calibration Time  |     | 0.5    |     | msec |

Table 9 Requirement for 32.768kHz crystal

# 3.7. Peripherals

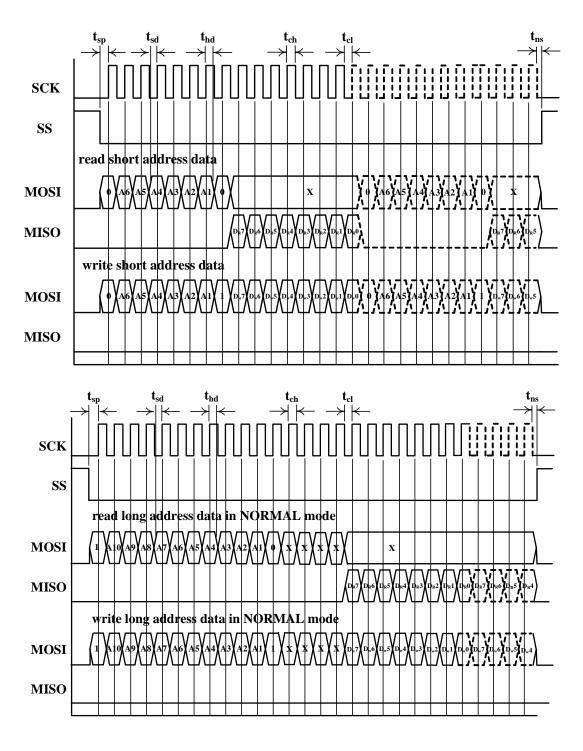

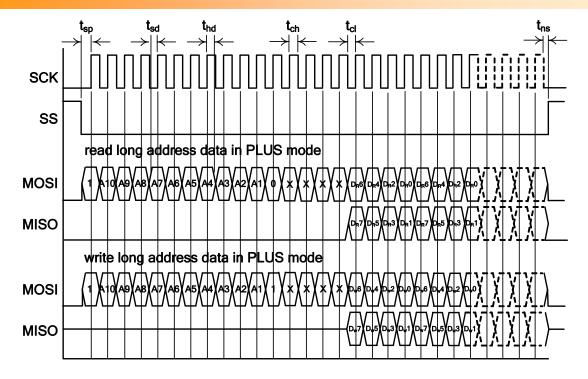

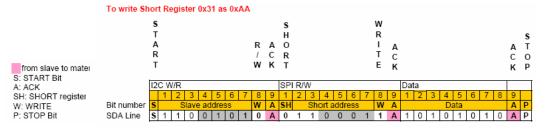

#### 3.7.1. SPI Interface

The SPI module provides slave roles SPI mode 0 interface to read/write the control registers, FIFO and security key table of UZ2400. The features are as below:

- Normal Mode: a simple 4-wire SPI-compatible interface (pins SCLK, SEN, SI and SO) where UZ2400 is the slave.

- Plus Mode: a 2x speed for long address read/write only. It uses SI & SO as SI0 & SI1 while writing long-address data, and as SO1 & SO0 while reading long-address data.

- Enhanced Mode: a 4x speed for long address read/write only. It uses SI, SO, GPIO5, & GPIO4 as SI0, SI1, SI2, & SI3 while writing long-address data, and as SO1, SO0, SO2, & SO3 while reading long-address data.

- Most significant bit (MSB) of all address and data transfer on the SPI interface is done first

- Mode selection: By default, SPI is set to normal mode. To select plus and enhanced modes, SReg0x34[7:6] should be set (by normal SPI operation) to 0x1 as plus mode, and 0x2 as enhanced mode. Afterward, plus or enhanced modes should be used.

#### SPI Characteristics

| Parameter                | Symbol            | Min  | Max | Units | Conditions                              |

|--------------------------|-------------------|------|-----|-------|-----------------------------------------|

| SCLK, clock frequency    | F <sub>SCLK</sub> |      | <10 | MHz   | 10MHz in normal/plus mode               |

|                          |                   |      | <5  |       | 5MHz in turbo mode                      |

| SCLK low pulse duration  | $t_CL$            | 50   |     | ns    | The minimum time SCLK must be low.      |

|                          |                   | 100  |     |       |                                         |

| SCLK high pulse duration | $t_{CH}$          | 50   |     | ns    | The minimum time SCLK must be high.     |

|                          |                   | 100  |     |       |                                         |

| SEN setup time           | $t_{SP}$          | 50   |     | ns    | The minimum time SEN must be low before |

|                          |                   |      |     |       | the first positive edge of SCLK.        |

| SEN hold time            | t <sub>NS</sub>   | >50  |     | ns    | The minimum time SEN must be held low   |

|                          |                   | >100 |     |       | after the last negative edge of SCLK.   |

| MOSI setup               | t <sub>SD</sub>   | 25   |     | ns    | The minimum time data must be ready at  |

|                          |                   |      |     |       | MOSI, before the positive edge of SCLK  |

| MOSI hold time           | t <sub>HD</sub>   | 25   |     | ns    | The minimum time data must be held at   |

|                          |                   |      |     |       | MOSI, after the positive edge of SCLK.  |

| Rise time                | t <sub>RISE</sub> |      | 25  | ns    | The maximum rise time for SCLK and SEN. |

| Fall time                | t <sub>FALL</sub> |      | 25  | ns    | The maximum fall time for SCLK and SEN. |

Table 10 SPI characteristics

# SPI Frame Format

Short Address Control Register (64 bytes)

| bit [7]            | bit [6:1]      | bit [0]           |

|--------------------|----------------|-------------------|

| Short Address<br>0 | $0x3F\sim0x00$ | Read/Write<br>0 1 |

Long Address Control Register (128 bytes)

| bit [11]     | bit [10:1]       | bit [0]           |

|--------------|------------------|-------------------|

| Long Address | $0x27F\sim0x200$ | Read/Write<br>0 1 |

Figure 21 FIFO addressing under SPI mode

# SPI Timing Diagrams

Figure 22 Timing diagram and specification in Normal Mode

Figure 23 Timing diagram and specification in Plus Mode (Only for long address registers)

Figure 24 Timing diagram and specification in Enhanced Mode (Only for long address registers)

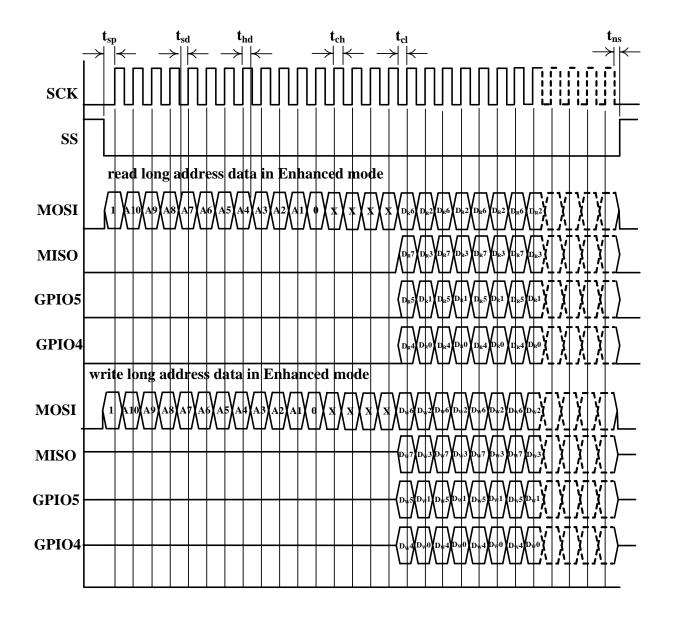

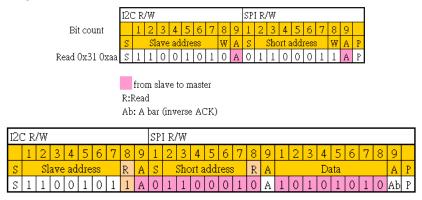

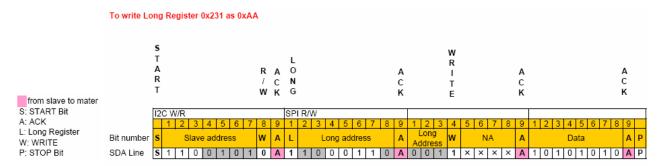

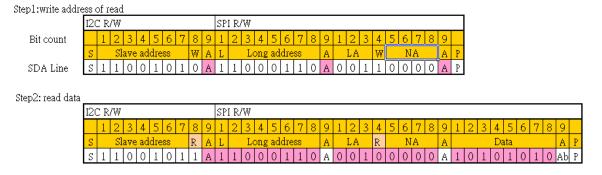

# 3.7.2. I<sup>2</sup>C Interface

UZ2400 provides another serial interface, I<sup>2</sup>C serial interface, to access the control registers and FIFOs.

# **Device Operation**

- CLOCK and DATA TRANSITIONS: The SDA/SCL pin is normally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods. Data changes during SCL high periods will indicate a start or stop condition as defined below.

- START CONDITION: A high-to-low transition of SDA with SCL high is a start condition which must precede any other command.

- STOP CONDITION: A low-to-high transition of SDA with SCL high is a stop condition.

- ACKNOWLEDGE: All addresses and data words are serially transmitted to and from the UZ2400 in 8-bit words. The UZ2400 sends a zero to acknowledge that it has received each word. This happens during the ninth clock cycle.

#### **Device Addressing**

The UZ2400 requires 7-bit device addresses plus control bits-over the two-wire serial bus following a start condition to enable the chip for a read or write operation. The device address word consists of 11001 for the first five most significant bits as shown below. The next 2 bits are  $b_2$  and  $b_1$  which are selected by SCLK and SEN pins respectively. The  $11001b_2b_1$  is the  $I^2C$  slave address of UZ2400. The programmable part  $b_2b_1$  of the address is defined by hardware pins SCLK and SEN respectively. The last bit  $b_0$  is a control bit. If  $b_0$  is LOW, it means "Write Operation" or else "Read Operation".

| SCLK | SEN | Slave Address |  |  |  |  |  |  |

|------|-----|---------------|--|--|--|--|--|--|

| 0    | 0   | 110 0100      |  |  |  |  |  |  |

| 0    | 1   | 110 0101      |  |  |  |  |  |  |

| 1    | 0   | 110 0110      |  |  |  |  |  |  |

| 1    | 1   | 110 0111      |  |  |  |  |  |  |

Table 11 I<sup>2</sup>C device address configuration

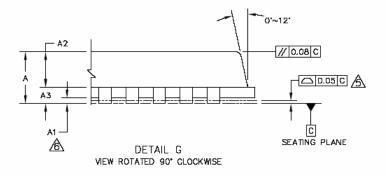

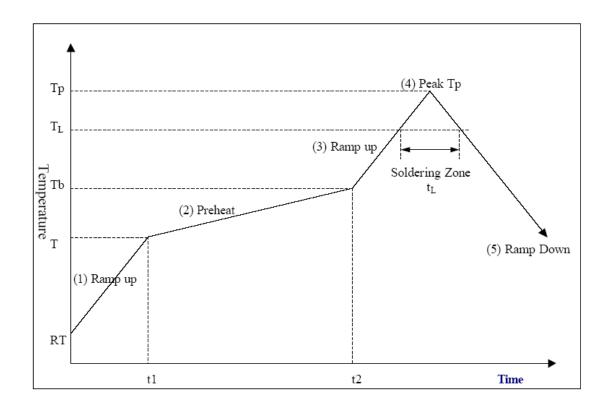

#### Write Operations